# Intel® Atom™ Processor and Intel® System Controller Hub US15W Development Kit

**User's Manual**

July 2008

Document #: 320264

Revision 1.0

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

$Contact\ your\ local\ Intel\ sales\ of fice\ or\ your\ distributor\ to\ obtain\ the\ latest\ specifications\ and\ before\ placing\ your\ product\ order.$

This document contains information on products in the design phase of development.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

$\ensuremath{^{*}\text{O}}$  ther names and brands may be claimed as the property of others.

Copyright © 2008 Intel Corporation. All rights reserved.

User's Manual 2

# **Contents**

| 1            | Introdu    | uction                                                              | 7 |

|--------------|------------|---------------------------------------------------------------------|---|

|              | 1.1<br>1.2 | About the Development Kit                                           |   |

|              | 1.3        | Technical Support                                                   | 9 |

|              | 1.4        | Product Literature                                                  |   |

|              | 1.5        | Related Documents                                                   |   |

| 2            | Crown      | Beach Board1                                                        | 1 |

|              | 2.1        | Getting Started1                                                    | 2 |

|              | 2.2        | Overview                                                            | _ |

|              | 2.3        | Major Features1                                                     |   |

|              | 2.4        | Processor Support1                                                  |   |

|              |            | 2.4.1 Processor Voltage Regulators                                  |   |

|              | 2.5        | Subsystem Descriptions                                              |   |

|              |            | 2.5.1 Intel® SCH Chipset                                            |   |

|              |            | 2.5.2 System Memory                                                 |   |

|              |            | 2.5.3 Display                                                       |   |

|              |            | 2.5.5 Soft Audio/Soft Modem                                         |   |

|              |            | 2.5.6 PATA Storage                                                  |   |

|              |            | 2.5.7 USB Connectors                                                |   |

|              |            | 2.5.8 LPC Slot1                                                     | 8 |

|              |            | 2.5.9 System Management Controller (SMC)/Keyboard Controller (KBC)1 |   |

|              |            | 2.5.10 EFI Firmware Hub (FWH)1                                      |   |

|              |            | 2.5.11 Trusted Platform Module (TPM) Header1                        |   |

|              |            | 2.5.12 SD/SDIO/MMC                                                  |   |

|              |            | 2.5.13 Clocks                                                       | _ |

|              |            | 2.5.14 Real Time Clock                                              |   |

|              |            | 2.5.15 In-Target Probe (ITP) and Debug Support                      |   |

|              |            | 2.5.17 Board Size                                                   |   |

|              |            | 2.5.17 Board Size                                                   |   |

|              |            | -,                                                                  |   |

| 3            |            | Management2                                                         |   |

|              | 3.1        | Power Measurement Support2                                          | 1 |

| 4            | Referer    | nce Board Summary2                                                  |   |

|              | 4.1        | Crown Beach Board Features2                                         |   |

|              | 4.2        | Connectors2                                                         |   |

|              |            | 4.2.1 Back Panel Connectors2                                        | 8 |

|              | 4.3        | Configuration Settings2                                             |   |

|              |            | 4.3.1 Configuration Jumpers/Switches2                               | 9 |

|              | 4.4        | BSEL Jumper Settings                                                | 2 |

| User's Manua | I          |                                                                     | 3 |

|            | 4.5    | Manual VID Support for CPU                                |    |

|------------|--------|-----------------------------------------------------------|----|

|            | 4.6    | Power On and Reset Push Buttons                           | 33 |

|            | 4.7    | LEDs                                                      | 34 |

|            | 4.8    | PCI Express* X1 Slots and Mini Card Connectors            | 35 |

|            |        | 4.8.1 Mini Card A connector (J7H1) is enabled by default  |    |

|            |        | 4.8.2 Mini Card B connector (J2G1) is disabled by default |    |

|            | 4.9    | H8S (JTAG) Programming Headers                            |    |

|            |        | 4.9.1 H8 In-System Programming                            |    |

|            | 4.10   | 4.9.2 H8 Remote Programming                               |    |

|            | 4.10   | UART Connector                                            | 38 |

| 5          | Quick  | Start                                                     | 39 |

|            | 5.1    | Required Peripherals                                      | 39 |

|            | 5.2    | Graphics Assembly (LVDS Panel)                            | 40 |

|            | 5.3    | Power Up                                                  |    |

|            | 5.4    | EFI Firmware Updates                                      | 45 |

| Appendix A | Daugh  | nter and Plug-In Cards                                    | 46 |

| A.1        | Mott C | Canyon 4 Interposer Card                                  | 46 |

| A.1.1      | Jumpe  | er Settings                                               | 47 |

| A.1.2      | Firmw  | vare Configuration                                        | 49 |

| Appendix B | Intel® | MVP-6 VID Codes                                           | 50 |

| Appendix C | Exterr | nal Features                                              | 53 |

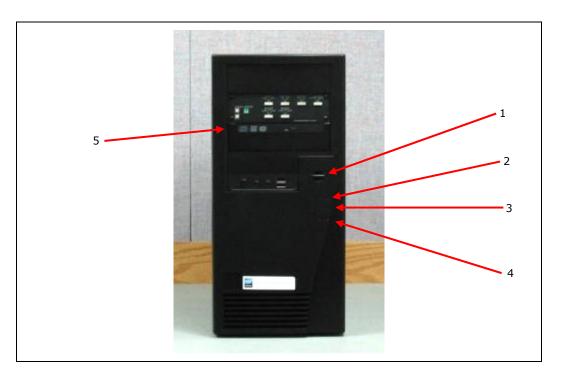

| C.1        | Exterr | nal Feature Locations                                     | 53 |

| C.1.1      | Exterr | nal Feature Location (Front of Chassis)                   | 53 |

| C 1 2      |        | nal Feature Location (Rear of Chassis)                    |    |

# **Figures**

**Tables**

| Figure 1. Crown Beach Board Block Diagram | 12<br>27<br>28<br>29<br>33<br>33<br>35<br>40<br>41<br>42<br>47<br>53       |

|-------------------------------------------|----------------------------------------------------------------------------|

| Table 1. Intel Literature Centers         | 10<br>13<br>17<br>21<br>22<br>28<br>30<br>32<br>34<br>35<br>36<br>38<br>48 |

User's Manual 5

# **Revision History**

| Document<br>Number | Revision<br>Number | Description                |

|--------------------|--------------------|----------------------------|

| 394649             | 1.0                | Initial release.           |

| 320264             | 1.0                | Release for public posting |

§

User's Manual 6

# 1 Introduction

This manual describes the typical hardware set-up procedures, features, and use of the evaluation board and other components included in the Intel® Atom $^{\text{TM}}$  processor and Intel® System Controller Hub US15W Development Kit. This reference board supports the Intel® Atom $^{\text{TM}}$  processor and Intel® System Controller Hub (Intel® SCH).

Note: Read this document in its entirety prior to applying power to the motherboard.

Intel recommends having both the schematic and board present while reading this document.

The references in this document correlate to reference designators and board properties of Crown Beach FAB F Customer Reference Board.

This manual is intended to be used with the Development Kit but can also be used to help bring up a Crown Beach Board, although not all associated peripherals will be included with a board.

# 1.1 About the Development Kit

The development kit includes the following:

- Crown Beach Customer Reference Board with Intel® Atom™ processor Z530 1.6GHz and Intel® System Controller Hub US15W

- Pre-installed jumpers

- FWH mounted and flashed with EFI

- 1 GB DDR2 SO-DIMM

- VGA SDVO ADD2N Card

- 80 GB Hard Drive with MIDINUX Embedded OS

- DVD-ROM Drive

- IDE cable

- Mott Canyon 4 with Intel® High Definition Audio (Intel® HD Audio) card

- Intel® 82574L Gigabit Ethernet Controller

- CD with Chipset and Intel® Embedded Graphics Drivers (IEGD)

- Chassis with ATX power supply

**Note:** Please refer to <u>Section 5.4</u> for the location of latest appropriate EFI firmware and driver updates.

User's Manual 7

*Note:* Not all peripherals listed will be included with a Crown Beach board.

# 1.2 Terminology

| Term            | Definition                                                                                       |

|-----------------|--------------------------------------------------------------------------------------------------|

| ACPI            | Advanced Configuration Power Interface                                                           |

| ADD2            | Advanced Digital display 2 card                                                                  |

| ADD2R           | Advanced Digital display 2 card with PCI-E graphics lane reversed (not supported on Crown Beach) |

| CRB             | Customer Reference Board                                                                         |

| BGA             | Ball Grid Array                                                                                  |

| DDR             | Double Data Rate                                                                                 |

| DMA             | Direct Memory Access                                                                             |

| Duck Bay 3      | PCI Express* interposer card that provides ExpressCard* support for Crown Beach CRB              |

| EFI             | Extensible Firmware Interface                                                                    |

| FAE             | Field Application Engineer                                                                       |

| FSB             | Front Side Bus                                                                                   |

| FWH             | Firmware Hub                                                                                     |

| GPIO            | General Purpose Input Output                                                                     |

| IDE             | Integrated Device Electronics                                                                    |

| IEGD            | Intel® Embedded Graphics Driver                                                                  |

| IMVP            | Intel® Mobile Voltage Positioning                                                                |

| Intel® HD Audio | Intel® High Definition Audio                                                                     |

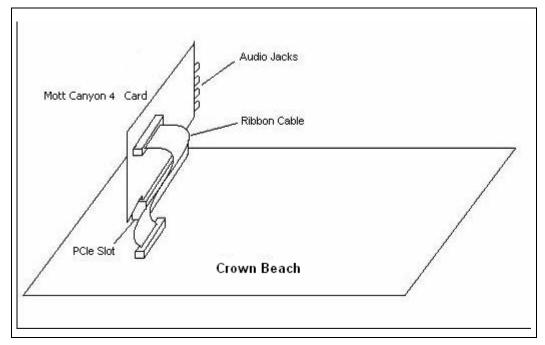

| Mott Canyon 4   | This Add-in Card enables Intel® HD Audio functionality                                           |

| Intel® SCH      | Intel® System Controller Hub                                                                     |

| ITP             | In-Target Probe                                                                                  |

| JEDEC           | Joint Electron Device Engineering Council                                                        |

| КВС             | Keyboard Controller                                                                              |

| LAN             | Local Area Network                                                                               |

| LED             | Light Emitting Diode                                                                             |

| LPC             | Low Pin Count                                                                                    |

| LVDS            | Low Voltage Differential Signaling                                                               |

| MDC             | Mobile Daughter Card                                                                             |

User's Manual 8

| Term    | Definition                               |

|---------|------------------------------------------|

| OS      | Operating System                         |

| PATA    | Parallel AT Attachment                   |

| PC      | Personal Computer                        |

| PCB     | Printed Circuit Board                    |

| PCIe*   | PCI Express*                             |

| PEG     | PCI Express* Graphics                    |

| PLL     | Phase Lock Loop                          |

| PGA     | Pin Grid Array                           |

| RTC     | Real Time Clock                          |

| SCH     | System Controller Hub                    |

| SD      | Secure Digital                           |

| SDVO    | Serial Digital Video Output              |

| SIO     | Super Input Output                       |

| SMC     | System Management Controller             |

| SO-DIMM | Small Outline Dual In-line Memory Module |

| TPM     | Trusted Platform Module                  |

| TSSOP   | Thin Shrink Small Outline Package        |

| USB     | Universal Serial Bus                     |

| VGA     | Video Graphics Array                     |

| VID     | Voltage Identification                   |

| VR      | Voltage Regulator                        |

| XDP     | Extended Debug Port                      |

# 1.3 Technical Support

Support Services for your hardware and software are provided through the secure Intel® Premier Support Web site at <a href="https://premier.intel.com">https://premier.intel.com</a>. After you log on, you can obtain technical support, review "What's New," and download any items required to maintain the platform. Support is provided through the following product: Dev Kit (Embedded/Atom/US15W).

# 1.3.1 Additional Technical Support

If you require additional technical support, please contact your field sales representative or local distributor.

User's Manual 9

## 1.4 Product Literature

You can order product literature from the following Intel literature centers.

**Table 1. Intel Literature Centers**

| U.S and Canada       | 1-800-548-4725    |  |  |

|----------------------|-------------------|--|--|

| U.S. (from overseas) | 708-296-9333      |  |  |

| Europe (U.K.)        | 44(0)1793-431155  |  |  |

| Germany              | 44(0)1793-421333  |  |  |

| France               | 44(0)1793-421777  |  |  |

| Japan (fax only)     | 81(0)120-47-88-32 |  |  |

## 1.5 Related Documents

$\underline{\text{Table 2}}$  is a partial list of the available collateral. For the complete list, contact your local Intel representative.

**Table 2. Related Documents.**

| Document                                                             | Document Numbers/ Location               |  |

|----------------------------------------------------------------------|------------------------------------------|--|

| Processor and SCH-Related Documents                                  |                                          |  |

| Intel® Centrino® Atom™ Processor Technology<br>Platform Design Guide | Contact your FAE for the latest revision |  |

| Menlow Platform Crown Beach Customer Reference<br>Board Schematic    |                                          |  |

| Menlow Platform – Ballout, Signal, and Mechanical<br>Package         |                                          |  |

| Intel® Atom™ Processor Z5xx Series Datasheet                         |                                          |  |

| Intel® System Controller Hub (Intel® SCH) Datasheet                  |                                          |  |

| Intel® Atom™ Processor Z5xx Series<br>Specification Update           |                                          |  |

| Intel® System Controller Hub (Intel® SCH)<br>Specification Update    |                                          |  |

| Firmware-Related Documents                                           |                                          |  |

| Aptio 4.x Whitepaper                                                 | www.ami.com/aptio/                       |  |

User's Manual 10

# 2 Crown Beach Board

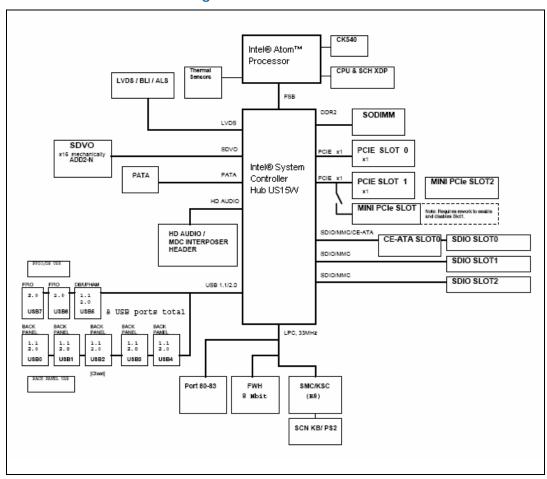

Figure 1. Crown Beach Board Block Diagram

User's Manual 11

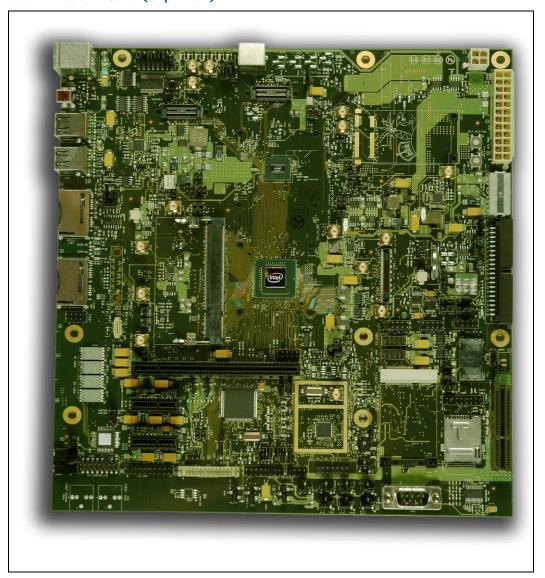

Figure 2. Crown Beach Board (Top View)

# 2.1 Getting Started

This section identifies the key components, features and specifications of the Intel® Atom $^{\text{TM}}$  processor with Intel® System Controller Hub US15W Development Kit. It also describes how to set up the board for operation. Development software is included in the kit.

User's Manual 12

**Note:** This manual assumes a familiarity with basic concepts involved with installing and configuring hardware for a PC.

#### 2.2 Overview

The development kit contains a baseboard with an Intel® Atom™ processor Z530, Intel® System Controller Hub US15W, other system board components and peripheral connectors.

**Note:** The evaluation board is shipped in a closed chassis. The user is required to observe extra precautions if the user opens the chassis for any reason.

**Note:** Review the document provided with the Development Kit titled Important Safety and Regulatory Information. This document contains additional safety warnings and cautions.

# 2.3 Major Features

<u>Table 3</u> is a list of the major features for the customer reference board.

**Table 3. Crown Beach Feature Set Summary**

| Feature                                   | Crown Beach Board<br>Implementation                                                                | Comments                                                                                              |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| Processor                                 | Intel® Atom™ processor Z530 with 512KB L2 cache                                                    | $0.55 \times 0.52$ inch (14 X 13 mm) FCBGA package with 0.0024 inch (0.6 mm) ball pitch and 441-pins. |  |

| CPU Voltage<br>Regulator                  | Intel® Mobile Voltage Positioning 6 (Intel® MVP6)  1 Phase                                         |                                                                                                       |  |

| Chipset                                   | Intel® SCH US15W  0.87 x 0.87 inch (22 X 22-mm) package with 0.0024 inch (0.6-pitch and 1249-pins. |                                                                                                       |  |

| Board<br>Technology                       | High Density Interconnect, Type IV; 1-6-1 stackup                                                  | S-G-S-G-Core-G-S-G-S stackup                                                                          |  |

| Board Size                                | μΑΤΧ 9.6 x 10.4 inch (243.84 x 264.16 mm)                                                          | Doubled-sided placement                                                                               |  |

| Memory                                    | Single top-side SO-DIMM connector for single-channel, single or dual rank                          | Supports up to 2-GB of system memory.<br>8 SDRAM devices max                                          |  |

| Graphics card slot. Supports ADD2N cards. |                                                                                                    | No integrated VGA support is available on the Crown Beach CRB. VGA supported through ADD2N Card.      |  |

User's Manual

| Feature                   | Crown Beach Board<br>Implementation                                                     | Comments                                                                                   |  |  |

|---------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| LVDS options              | Single 24-bit LVDS interface;<br>Back Light Inverter (BLI) and<br>LED backlight support | Through a 50-pin cable-up connector (separate cables required for each display supported). |  |  |

| Main Clock                | CK540                                                                                   | TSSOP, 64-pinspackage Integrated CK-SSCD and clock expansion buffer.                       |  |  |

| ATA/Storage               | PATA66/100                                                                              | One desktop PATA connector                                                                 |  |  |

| USB                       | 8 USB 2.0 ports                                                                         | 4 back panel connectors                                                                    |  |  |

| SDIO/MMC                  | 2 ports (Ports 0 and 1), 4-bits<br>1 port (Port 2), 8-bits                              | 2 SDIO back panel connectors                                                               |  |  |

| Soft Audio/ Soft<br>Modem | 2 x8 option for cable-up to SDVO<br>for HDMI+<br>One Intel® HD Audio MDC<br>Header      | Option for 3.3-V and 1.5-V operation through jumper.  2 x4 for Mott Canyon 4 support       |  |  |

| PCI Express* x1 connector | 2 connectors                                                                            | x1 connector  Revision 1.0a compliant  NOTE: Slot 1 is non-functional by default.          |  |  |

| Feature                                | Crown Beach Board<br>Implementation                                                                                                         | Comments                                                                      |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| PCI Express*<br>Mini Card<br>connector | 2 connectors.  Mini Card connector A, functionality is enabled by default.  NOTE: PCI Express* signals are left unconnected on Mini Card B. | NOTE: For more information, refer to Section 2.5.4, PCI Express* Slots.       |  |  |

| LPC                                    | One LPC slot                                                                                                                                | No DMA support                                                                |  |  |

| TPM                                    | Through TPM header (TPM 1.2)                                                                                                                |                                                                               |  |  |

| Microcontroller                        | Renesas Technology* H8S/2117                                                                                                                | Includes integrated SPI as an option                                          |  |  |

| FWH                                    | FWH LPC based with socket                                                                                                                   | 40-pin TSSOP socket                                                           |  |  |

| SIO                                    | Uses TPM header                                                                                                                             | Backup only; provides floppy, COM,<br>Parallel, and PS2                       |  |  |

| SMC/KBC                                | Scan matrix headers and PS/2 in back panel keyboard connector                                                                               | ACPI compliant through H8S/2117                                               |  |  |

| RTC                                    | Battery-backed real time clock                                                                                                              |                                                                               |  |  |

| Port 80 Decode                         | Supported down on motherboard with four seven-segment displays                                                                              | Has an option for cable-up to front panel of chassis                          |  |  |

| Power Supply                           | Desktop Mode                                                                                                                                | ATX Power Supply                                                              |  |  |

| rower Supply                           | Virtual Battery                                                                                                                             | SW8A1 switch                                                                  |  |  |

| ITP Support                            | Extended Debug Port (XDP)                                                                                                                   | J1E3 XDP connector                                                            |  |  |

| Power<br>Management<br>Form Factor     | ACPI Compliant                                                                                                                              | S0 - Power On<br>S3 - Suspend to RAM<br>S4 - Suspend to Disk<br>S5 - Soft Off |  |  |

# 2.4 Processor Support

The reference board supports the Intel® Atom™ processor Z530 with 512-KB cache in a 441-pin, FCBGA package. No heatsink is required by this processor during room temperature ambient operation.

## 2.4.1 Processor Voltage Regulators

The reference board uses an onboard Intel® MVP6 single-phase regulator for the processor core supply. The I/O voltage is 1.05 V. See Section 4.5 for VID jumper location and Appendix B for the VID code table.

User's Manual 15

# 2.5 Subsystem Descriptions

Subsystem features refer to the socket and connector locations on the Crown Beach Board. Socket and connector locations are labeled with a letter-number combination. Refer to the silkscreen labeling on Crown Beach Board for location detail.

#### 2.5.1 Intel® SCH Chipset

- Processor interface at 400/533 MHz

- Single channel DDR2 memory interface running at 400/533 MT/s

- Two PCI Express\* ports, x1

- Eight USB 2.0 compatible ports

- One ATAPI-6 (UDMA 100MB/s) IDE channel

- Intel® HD Audio

- Three SDIO/MMC interfaces

- One channel 24-bit LVDS

- One channel SDVO

- LPC bus

#### 2.5.2 System Memory

- Supports a single DDR2 SO-DIMM socket. SO-DIMMs must be un-buffered and compliant with Raw Cards A or C as defined by JEDEC.

- Supports 400- or 533-MHz memory bus frequencies.

Note: SO-DIMM support is only provided for validation purposes. The Intel® Centrino® Atom™ Processor Technology Platform Design Guide provides component implementations for memory down solutions. The DDR2 SODIMM Architecture's Implementation for Intel® System Controller Hub (SCH) US15W whitepaper provides guidelines for implementing a SO-DIMM solution, although the recommendations are based on simulation only and have not been validated. It is recommended that customers validate their designs.

#### 2.5.3 Display

The reference board has two options for displaying video:

- LVDS location is J5G2

- SDVO location is J7C2

Note: The customer reference board supports single channel LVDS only.

Table 4 is a listing of displays that have been tested with Crown Beach.

User's Manual 16

**Table 4. Crown Beach Supported LVDS Displays**

| Manufacturer<br>/Type | Size                     | Resolution | Back<br>Light | Aspect<br>Ratio | Part#          |

|-----------------------|--------------------------|------------|---------------|-----------------|----------------|

| Samsung               | 4.8 inch<br>(121.92 mm)  | 1024 x 600 | 11 LED        | 16 x 9          | LTS480WS-C01   |

| TMD                   | 5.6 inch<br>(142.24 mm)  | 1024 x 600 | CCFL          | 16 x 9          | LTD056ET0S     |

| Sharp                 | 7.2 inch<br>(182.88 mm)  | 1280 x 768 | 32 LED        | 15 x 9          | LQ072K1LA08    |

| Samsung               | 15 inch<br>(381.00 mm)   | 1024 x 768 | CCFL          | 4 x 3           | LTN150XG-L08   |

| NEC                   | 8.4 inch<br>(213.36 mm)  | 640 x 480  | 2 CCFL        | 4 x 3           | NL6448BC26-08D |

| NEC                   | 9.0 inch<br>(228.60 mm)  | 800 x 480  | 2 CCFL        | 15 x 9          | N8048BC24-06   |

| TMD                   | 11.1 inch<br>(281.94 mm) | 1366 x 768 | CCFL          | 16 x 9          | LTD111EXCS     |

| Samsung               | 15.4 inch<br>(391.16 mm) | 1280 x 800 | CCFL          | 15 x 9          | LTN154X5-L06   |

**NOTE:** The protective tape on top of the Crown Beach LVDS connector must be removed prior to installing an LVDS cable.

**NOTE:** VGA output is not directly supported. Customers can use PCI Express\*-based discrete, external 3D graphics cards, or a third-party component available on an ADD2N card using the SDVO interface.

#### 2.5.4 PCI Express\* Slots

- Two PCI Express\* slots x1 for add-in cards.

- The PCI Express\* bus complies with the PCI Express\* Rev. 1.0a specification.

Crown Beach provides two PCI Express\* Mini Card form factor slots. The PCI Express\* specification pin-out is followed by Mini Card Slot A only and not by Mini Card Slot B. Mini Card Slot A is enabled by default and to enable Mini Card Slot B, rework needs to be performed. The slots are not to be used with PCI Express\* Mini Card-based devices. Mini Card A (J7H1) is designed for use with CM100/CM101 cards from Quanta. Mini Card A can be populated with the Kedron, Echo Peak, or Shirley Peak wireless cards. Mini Card B (J2G1) is designed for use with Wireless WAN cards from Sierra Wireless\* and Option\*.

#### 2.5.5 Soft Audio/Soft Modem

High Definition Soft Audio/Soft Modem functionality is enabled through the Mott Canyon 4 daughter card. No direct connection is provided for Intel® HD Audio on

User's Manual 17

Crown Beach. The Mott Canyon 4 card is required to enable the High Definition Audio functionality. See Appendix A for more information on the Mott Canyon 4 card.

## 2.5.6 PATA Storage

The Crown Beach Board provides only one desktop, 40-pin, PATA66/100 connector that supports master and slave devices.

#### 2.5.7 USB Connectors

The Intel® SCH provides eight USB 2.0 ports.

- Four ports are routed to the back panel's two stacked USB connectors. USB ports [1:0] and [4:3] are routed to the back of the chassis.

- Port 2 is the client-mode connector and is routed to the back of the chassis with a Mini-B connector.

- Ports [7:5] are routed to the front panel headers (USB FPIO, Duck Bay, and Sideband Header) and to the Sideband headers (Duck Bay, Upham USB).

- For wireless solutions port 0 is also used with stuffing options for the PCI Express\* Mini Card. OC [7:0] # is available for over-current detection.

- Port 5 is disabled by default due to enabling of PCI Express\* Mini Card A Slot.

**Note:** USB port 0 functionality is impacted if rework is performed to enable the PCI Express\* Mini Card B Slot.

#### 2.5.8 **LPC Slot**

The H8S/2117 serves as a keyboard controller on the customer reference board.

**Note:** Other solutions, such as a mouse controller, can be tested in the LPC slot while H8S is held in reset.

- LPC slot and sideband header are supported.

- Docking and DMA are not supported by the Intel® SCH on Crown Beach.

- Port 80-83 is implemented using the EPM7064AE device down on the motherboard with 4, seven-segment displays on the LPC bus.

- An option for connecting the cable to front panel or chassis is available.

# 2.5.9 System Management Controller (SMC)/Keyboard Controller (KBC)

Renesas Technology\* H8S serves as both SMC and KBC for the platform. The SMC/KBC controller supports:

User's Manual 18

• Two PS/2 ports.

**Note:** The two PS/2 ports are for a legacy keyboard and mouse. The keyboard plugs into the bottom port and the mouse plugs into the top port.

- EMA support

- Wake/runtime SCI events

- Power sequencing control

#### 2.5.10 EFI Firmware Hub (FWH)

A TSOP socket houses the flash device (ST Microelectronics P/N# M50FW080) that stores the system EFI firmware. The EFI firmware can be programmed through a Microsoft MS-DOS\* or Windows\*-based utility.

#### 2.5.11 Trusted Platform Module (TPM) Header

Crown Beach implements a header at J9B4 to support TPM 1.2 specification compliant devices. The same header can be used for legacy connections, allowing other SIO solutions to provide floppy, COM, Parallel, and PS/2 functionality.

#### 2.5.12 SD/SDIO/MMC

Crown Beach provides three ports with the following features:

- All ports are SD rev1.1 specification compliant and MMC rev4.0 specification compliant.

- All ports operate to 48 MHz. Ports 0 and 1 support 4-bit operation. Port 2 supports 8-bit operation.

- Slot 2 is also routed (with stuffing options) to the PCI Express\* Mini Card for wireless solutions.

#### 2.5.13 Clocks

The Crown Beach CRB uses a CK-540 clock solution. The BSEL [2:1] signals driven by the processor are used by the CK-540 to configure the FSB frequency.

#### 2.5.14 Real Time Clock

An on-board battery maintains power to the real time clock (RTC) when in a mechanical off state (G3 state).

User's Manual

## 2.5.15 In-Target Probe (ITP) and Debug Support

Crown Beach provides on-board ITP support with an XDP connector. Users can debug from the reset vector without EFI or OS dependency (up to OS functionality). Ports 80-83 are provided as a troubleshooting tool to monitor POST output during EFI execution.

**Note:** ITP requires that the CMC load to configure Poulsbo before register accesses can be made. The CMC code resides in the FWH on Crown Beach. Thus, it is required that the FWH flash be programmed and inserted in the FWH socket to use ITP.

Note: Crown Beach does not support ITP 700.

#### 2.5.16 Power Supply Solution

Crown Beach can be powered from an ATX power supply (desktop solution) that contains all of the voltage regulators necessary to power the system up. Additionally, virtual battery support is provided through switch SW8A1.

Note: Use an "ATX12V" 1.1 specification compliant power supply regardless of supplier or wattage level (an "ATX12V" rating means V5 min current = 0.1 A, "ATX" V5 min current = 1.0 A, among other differences). For example, the Sparkle Model No. FSP300-60BTV meets this requirement and is an ATX12V 1.1 spec compliant power supply. Depending on the power supply used, Crown Beach may require a load. Crown Beach provides FETS to assist with this loading through jumpers J4J1 and J5J2, see Table 9 for jumper settings.

**Note:** If the power switch on the ATX power supply is used to shut down the system, wait at least 5 seconds before turning the system on again.

**Note:** The recommended way to shut down the board is to press and hold the power button switch (SW3J1) for 5 seconds until the power supply turns off. Using the power supply switch or pulling the plug out of the wall is not recommended.

#### 2.5.17 Board Size

The reference board form factor is similar to the  $\mu$ ATX 9.6 x 10.4 inch (243.84 x 264.16 mm) specification. The back panel jacks may not conform to ATX specifications.

#### 2.5.18 Board Technology

The Crown Beach reference board uses fine pitched BGA packages, down to 0.0024 inch (0.6 mm) pitch. Type IV high density-interconnect technology is required for breakout purposes and implemented using a 1-6-1 stack-up (8 layers total).

ξ

User's Manual 20

# 3 Power Management

# 3.1 Power Measurement Support

Power measurement resistors are provided to measure the power on many of the subsystems.

**Table 5. Power Measurement Resistor**

| Feature   | Value |

|-----------|-------|

| Tolerance | 1%    |

| Value     | 10 mΩ |

**NOTE**: Intel recommends that larger ( $\sim$ 10 m $\Omega$ ) resistors be stuffed for greater accuracy.

Power on a particular subsystem is calculated using the following formula:

#### Equation 1.

$$P = \frac{V^2}{R}$$

R = value of the sense resistor (typically 0.01  $\Omega$ )

V = the voltage difference measured across the sense resistor.

Use a high precision digital multi-meter tool such as the Agilent 34401A digital multi-meter. Refer to <u>Table 6</u> for a comparison of a high-precision, digital multi-meter (Agilent 34401A) versus a precision, digital multi-meter (Fluke 79).

Table 6. Digital Multi-Meter Comparison

| Example System                     |                     |  |  |  |  |

|------------------------------------|---------------------|--|--|--|--|

| Sense Resistor Value               | 0.01 Ω              |  |  |  |  |

| Voltage Difference Across Resistor | 1.492 mV (149.2 mA) |  |  |  |  |

| Calculated Power                   | 0.223 mW            |  |  |  |  |

|                                    |                     |  |  |  |  |

User's Manual 21

|                                           | Agilent 34401A (6½ digit display)                                            | Fluke 79 (3 digit display) |

|-------------------------------------------|------------------------------------------------------------------------------|----------------------------|

| Specification                             | $(\pm 0.0030 \% \text{ of reading})$<br>+ $(\pm 0.0030 \% \text{ of range})$ | ±0.09% ±2 digits           |

| Min Voltage displayed<br>Calculated power | 1.49193 mV<br>0.22258 mW                                                     | 1.47 mV<br>0.216 mW        |

| Max voltage displayed<br>Calculated power | 1.49206 mV<br>0.22624 mW                                                     | 1.51 mV<br>0.228 mW        |

| Error in power                            | ±0.009 %                                                                     | ±0.3 %                     |

**NOTE:** The precision achieved by using a high precision digital multi-meter versus a normal digital multi-meter is  $\sim 33$  times more accurate.

<u>Table 7</u> summarizes all the power measurement sense resistors located on the Crown Beach board. All sense resistors are  $0.01~\Omega$  unless otherwise noted.

**Table 7. Crown Beach Voltage Rails**

| Sch Page | Component | Voltage | Supply      | Rail              | Ref Des | Resistor    | Supply<br>Power<br>Topology |

|----------|-----------|---------|-------------|-------------------|---------|-------------|-----------------------------|

| 11       | SCH       | 1.8 V   | +V1.8       | +V1.8_SM_SCH      | R5T3    | 0.01,<br>1% | DDR2_VR                     |

| 11       | SCH       | 1.05 V  | +V1.05S_SCH | +V1.05S_SCH_VCORE | R6T7    | 0.01,<br>1% | VCORE                       |

| 11       | SCH       | 1.5 V   | +V1.5S_SCH  | +V1.5S_DLVDS_SCH  | R6T9    | 0.01,<br>1% | LVDS                        |

| 11       | SCH       | 3.3 V   | +V3.3       | +V3.3_SCH_SUS     | R6T13   | 0.01,<br>1% | SUS                         |

| 11       | SCH       | 3.3 V   | +V3.3S      | +V3.3S_SCH        | R5T5    | 0.01,<br>1% | 3.3 V                       |

| 11       | SCH       | 1.05 V  | +V1.05S_VTT | +V1.05S_VTT_SCH   | R5U35   | 0.01,<br>1% | VTT SCH                     |

| 11       | SCH       | 1.5 V   | +V1.5S      | +V1.5S_SCH        | R5T6    | 0.01,<br>1% | 1.5CORE                     |

| 11       | SCH       | 1.5 V   | +V1.5S_SCH  | +V1.5S_SDVO_SCH   | R6T10   | 0.01,<br>1% | SDVO                        |

| 11       | SCH       | 1.05 V  | +V1.05S_VTT | +V1.05S_VTT_CPU   | R3U1    | 0.01,<br>1% | VTT CPU                     |

User's Manual 22

| Sch Page | Component     | Voltage         | Supply        | Rail                                                                                                    | Ref Des | Resistor    | Supply<br>Power<br>Topology |

|----------|---------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------|---------|-------------|-----------------------------|

| 11       | SCH           | 1.5 V           | +V1.5S_SCH    | +V1.5S_PCIe_SCH                                                                                         | R6T6    | 0.01,<br>1% | PCIe*                       |

| 11       | SCH           | 1.8 V           | +V1.8         | +V1.8_SM_SCH                                                                                            | R5T3    | 0.01,<br>1% | DDR2_VR                     |

| 12       | SCH           | 1.5 V           | +V1.5S_SCH    | +V1.5S_DPLLA_SCH,<br>+V1.5S_DPLLB_SCH,<br>+V1.5S_PCIePLL_SCH,<br>+V1.5S_HPLL_SCH,<br>+V1.5S_AUSBPLL_SCH | R6T1    | 0.01,<br>1% | PLLs                        |

| 14       | mini PCIe     | 1.5 V           | +V1.5S        | V1.5S_MINIPCIE                                                                                          | R7W9    | 0.01,<br>1% | 1.5-V mini PCIe             |

| 14       | mini PCIe     | 3.3 V           | +V3.3         | V3.3_MINIPCIE                                                                                           | R9F1    | 0.01,<br>1% | 3.3-V aux mini<br>PCIe      |

| 15       | SDVO          | 3.3 V           | +V3.3S        | V3.3S_SDVO                                                                                              | R7C1    | 0.01,<br>1% | 3.3-V SDVO                  |

| 16       | SDVO          | 12 V            | +V12S         | V12S_SDVO                                                                                               | R7B3    | 0.01,<br>1% | 12-V SDVO                   |

| 17       | LVDS          | 3.3 V           | +V3.3S        | V3.3S_LVDS_DDC                                                                                          | R5V21   | 0.01,<br>1% | 3.3-V<br>LVDS_DDC           |

| 17       | LVDS          | 5 V             | +V5S          | V3.3S_LVDSBKLT                                                                                          | R5V14   | 0.01,<br>1% | 5-V<br>LVDS_BCKLT           |

| 17       | LVDS          | 12 V            | +V12S         | V12S_LVDSBKLT                                                                                           | R5V17   | 0.01,<br>1% | 12-V<br>LVDS_BCKLT          |

| 17       | LVDS          | 3.3 V           | +V3.3S        | V3.3S_LVDS_VDL                                                                                          | R5V28   | 0.01,<br>1% | 3.3-V<br>LVDS_VDL           |

| 18       | SO_DIMM       | 1.8 V           | +V1.8         | +V1.8_DIMM                                                                                              | R6R2    | 0.01,<br>1% | SO-DIMM_DDR2                |

| 20       | FHW           | 3.3 V           | +V3.3S        | +V3.3S_FWH                                                                                              | R7H5    | 0.01,<br>1% | 3.3-V_FWH                   |

| 21       | TPM           | 5 V             | +V5           | V5_TPM                                                                                                  | R8N4    | 0.01,<br>1% | 5-V TPM<br>HEADER           |

| 21       | TPM           | 3.3 V           | +V3.3         | V3.3A_TPM                                                                                               | R8P2    | 0.01,<br>1% | 3.3-V TPM<br>HEADER         |

| 21       | MDC,<br>Audio | 3.3 V           | +VCCHDA       | VCCHDA_R                                                                                                | R8U3    | 0.01,<br>1% | 3.3V MDC<br>HEADER          |

| 21       | MDC,<br>Audio | 1.5 V/<br>3.3 V | +V1.5S/+V3.3S | VCC_MDC                                                                                                 | R9E1    | 0.01,<br>1% | 1.5-V/3.3-V<br>MDC HEADER   |

| Sch Page | Component       | Voltage | Supply               | Rail              | Ref Des | Resistor    | Supply<br>Power<br>Topology             |

|----------|-----------------|---------|----------------------|-------------------|---------|-------------|-----------------------------------------|

| 21       | TPM             | 3.3 V   | +V3.3S               | V3.3S_TPM         | R8P1    | 0.01,<br>1% | 3.3-V TPM<br>HEADER                     |

| 22       | PCIe,<br>slot0  | 12 V    | +V12_SLOTS           | V12S_PCIE_SLOT0   | R8B1    | 0.01,<br>1% | 12-V PCIe slot 0                        |

| 22       | PCIe,<br>slot0  | 3.3 V   | +V3.3_SLOTS          | V3.3S_PCIE_ SLOT0 | R8C2    | 0.01,<br>1% | 3.3-V PCIe<br>slot 0                    |

| 22       | PCIe,<br>slot1  | 12 V    | +V12_SLOTS           | V12S_PCIE_ SLOT1  | R8B3    | 0.01,<br>1% | 12-V PCIe slot 1                        |

| 22       | PCIe,<br>slot1  | 3.3 V   | +V3.3_SLOTS          | V3.3S_PCIE_ SLOT1 | R8C5    | 0.01,<br>1% | 3.3-V PCIe<br>slot 1                    |

| 22       | PCIe,<br>slot0  | 3.3 V   | +V3.3                | V3.3_PCIE_ SLOT0  | R8C6    | 0.01,<br>1% | 3.3-V AUX PCIe<br>slot 0                |

| 22       | PCIe,<br>slot1  | 3.3 V   | +V3.3                | V3.3_PCIE_ SLOT 1 | R8C7    | 0.01,<br>1% | 3.3-V AUX PCIe<br>slot 1                |

| 23       | USB             | 5 V     | +V5                  | +V5_USB_P6_P7     | R6H2    | 0.01,<br>1% | 5-V USB Port 6<br>and 7                 |

| 23       | USB             | 5 V     | +V5                  | +V5_USB_P5        | R6H3    | 0.01,<br>1% | 5-V USB Port 5                          |

| 24       | CK540           | 3.3 V   | +V3.3S               | V3.3S_CK505       | R8U1    | 0.01,<br>1% | 3.3-V CK505                             |

| 25       | SDIO1           | 3.3 V   | V3.3S_SDIO_<br>SLOT1 | V3.3S_SDIO1       | R5M1    | 0.01,<br>1% | 3.3-V SDIO 1                            |

| 25       | SDIO0           | 3.3 V   | V3.3S_SDIO_<br>SLOT0 | V3.3S_SDI00       | R6N1    | 0.01,<br>1% | 3.3-V SDIO 0                            |

| 25       | SDIO2           | 3.3 V   | V3.3S_SDIO_<br>SLOT2 | V3.3S_SDIO2       | R4B1    | 0.01,<br>1% | 3.3-V SDIO 2                            |

| 27       | H8/<br>Keyboard | 3.3 V   | +V3.3A               | +V3.3A_KBC        | R7E2    | 0.01,<br>1% | 3.3-V<br>KEYBOARD                       |

| 31       | HD Conn         | 5 V     | +V5S                 | +V5S_PATA         | R3J1    | 0.01,<br>1% | 5-V HD<br>Connector                     |

| 32       | USB             | 5 V     | +V5                  | +V5_USB_P0_P1     | R2N1    | 0.01,<br>1% | 5-V USB Port 0<br>and 1 (Back<br>Panel) |

| 32       | USB             | 5 V     | +V5                  | +V5_USB_P3_P4     | R3N1    | 0.01,<br>1% | 5-V USB Port 3<br>and 4 (Back<br>Panel) |

| Sch Page | Component                | Voltage | Supply    | Rail              | Ref Des | Resistor     | Supply<br>Power<br>Topology                                     |

|----------|--------------------------|---------|-----------|-------------------|---------|--------------|-----------------------------------------------------------------|

| 33       | 1.05-V<br>Dual VR<br>(2) | 12 V    | +V12S     | V1.05B_INPUT      | R5G1    | 0.01,<br>1%  | 1.05-V Dual VR<br>(1)><br>+V1.05S_VTT,<br>+V1.05S_VTT_C<br>PU   |

| 33       | 1.05-V<br>Dual VR<br>(1) | 12 V    | +V12S     | V1.05A_INPUT      | R5V9    | 0.01,<br>1%  | 1.05-V Dual VR<br>(2)><br>+V1.05S_SCH,<br>+V1.05S_SCH_<br>VCORE |

| 36       | 1.8-V VR<br>(1)          | 12 V    | +V12      | V12_1.8_INPUT     | R5C16   | 0.01,<br>1%  | 1.8-V VR (1)<br>> +V1.8                                         |

| 36       | 0.9-V VR<br>(2)          | 12 V    | +V0.9S    | V0.9S_DDR2        | R5R2    | 0.01,<br>1%  | 1.8-V VR (2)<br>> +V0.9                                         |

| 38       | 1.5-V VR                 | 3.3 V   | +V3.3S    | V3.3S_1.5_INPUT   | R5F18   | 0.01,<br>1%  | 1.5-V VR><br>+V1.5S                                             |

| 39       | 3.3-V VR                 | 3.3 V   | +V3.3A    | 51120VBST2_LR     | R4G14   | 0.002,<br>1% | 3.3-V VR                                                        |

| 39       | 3.3-V VR                 | 3.3 V   | +V12A     | V12A_3.3A_INPUT   | R3W1    | 0.01,<br>1%  | 3.3-V VR                                                        |

| 39       | 5-V VR                   | 5 V     | +V12A     | V12A_5A_INPUT     | R4W4    | 0.01,<br>1%  | 5-V VR                                                          |

| 39       | 5V VR                    | 5 V     | +V5A      | 51120_+V5A_MBL_QL | R4H3    | 0.002,<br>1% | 5-V VR                                                          |

| 41       | Intel®<br>MVP-6          | 5 V     | +V5S      | V5S_IMVP_IN       | R3C9    | 0.01,<br>1%  | Intel MVP-6                                                     |

| 42       | Intel®<br>MVP-6          | 12 V    | +V12S_CPU | V12_CPU_PHASE     | R2R8    | 0.002,<br>5% | Intel MVP-6                                                     |

| 44       | ATX Conn                 | 12 V    | +V12A     | +V12_ATX          | R1J3    | 0.002,<br>5% | 12-V ATX conn                                                   |

| 45       | S4                       | 5 V     | +V5       | +V5A              | R4G9    | 0.01,<br>1%  | 5 V, S4                                                         |

| 45       | S4                       | 3.3 V   | +V3.3     | +V3.3A            | R4G12   | 0.01,<br>1%  | 3.3 V, S4                                                       |

| 45       | S3                       | 5 V     | +V5S      | +V5A              | R4F4    | 0.002,<br>1% | 5 V, S3                                                         |

| 45       | S3                       | 3.3 V   | +V3.3S    | +V3.3A            | R4G10   | 0.01,<br>1%  | 3.3 V, S3                                                       |

| Sch Page | Component | Voltage | Supply | Rail      | Ref Des | Resistor    | Supply<br>Power<br>Topology |

|----------|-----------|---------|--------|-----------|---------|-------------|-----------------------------|

| 45       | S3        | 12 V    | +V12S  | +V12S_CPU | R1H2    | 0.01,<br>1% | 12 V, S3                    |

§

User's Manual 26

# 4 Reference Board Summary

#### 4.1 Crown Beach Board Features

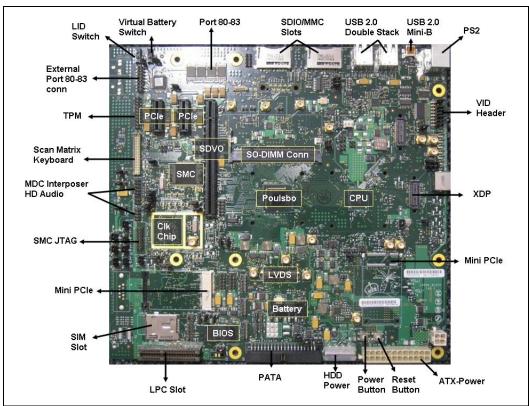

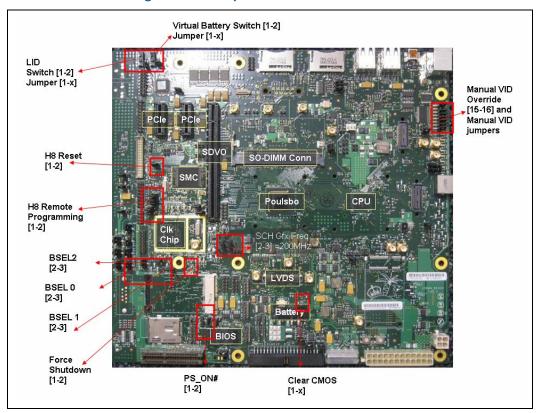

Figure 3. Crown Beach Board Feature Placement

Note: The actual labeling on the board is Port 80 and 81.

#### 4.2 Connectors

Many of the connectors supply operating voltages of  $(+5V\ DC\ and\ +12V\ DC)$  to devices inside the computer chassis, such as fans and internal peripherals.

**Caution:** Most of these connectors are not over-current protected. Do not use these connectors for powering devices external to the computer chassis. A fault in the load presented

User's Manual 27

by the external devices could damage the computer, the interconnecting cable, or the attached external device.

#### 4.2.1 Back Panel Connectors

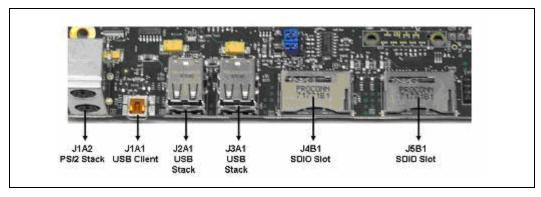

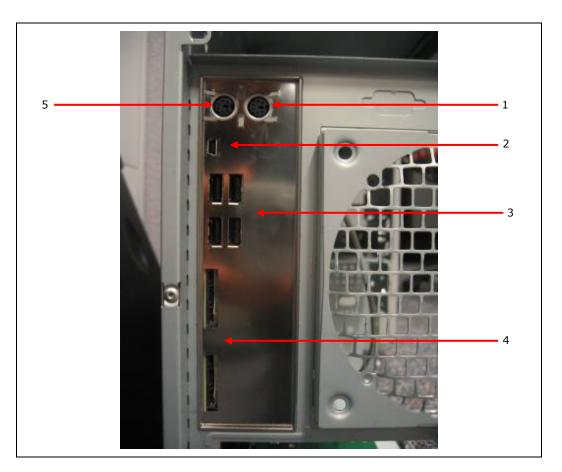

This section describes the board's connectors.  $\underline{\text{Figure 4}}$  shows the location of the back panel connectors on the board.

**Figure 4. Back Panel Connectors**

Note: Connector J1A1 USB Client is a USB 2.0 Mini-B connector.

**Table 8. Back Panel Connectors**

| Ref Des  Back Panel Connector | Description                                                           |

|-------------------------------|-----------------------------------------------------------------------|

| J1A2                          | PS/2 connector Top: Mouse Bottom: Keyboard                            |

| J1A1                          | USB Client connector, Port 2                                          |

| J2A1                          | USB Host ports with over-current detection Top: Port 0 Bottom: Port 1 |

| J3A1                          | USB Host ports with over-current detection Top: Port 4 Bottom: Port 3 |

| J4B1                          | 8-bit SD/SDIO/MMC Slot 2                                              |

| J5B1                          | 4-bit SD/SDIO/MMC Slot 1                                              |

User's Manual 28

# 4.3 Configuration Settings

#### 4.3.1 Configuration Jumpers/Switches

#### Caution:

Do not move jumpers with the power on. Switches may be moved while power is on. Always turn off the power and unplug the power cord from the computer before changing jumper settings. Otherwise, damage to the board could occur.

<u>Figure 5</u> shows the location of the major configuration jumpers and switches. <u>Table 9</u> summarizes the jumpers and switches and gives their default and optional settings. The Crown Beach board is shipped with the jumpers and switches shunted in the default locations.

Figure 5. Location of the Configuration Jumpers/Switches

User's Manual 29

Table 9. Configuration Jumper/Switches Settings

| #  | Description                                                                                                                | Default Setting <sup>1</sup>                                                                                                  | Optional Setting                                                                                                                                                    | Reference<br>Designator |

|----|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1a | Remote H8<br>Programming                                                                                                   | Open                                                                                                                          | 1-2 (Short) – to<br>program H8 <sup>3</sup>                                                                                                                         | J8E1<br>J8E4            |

| 1b | Remote H8<br>Programming<br>(BB_PROG)                                                                                      | 1-2 – normal operation                                                                                                        | 1-x – link the Host Unit<br>to On Board H8                                                                                                                          | J8D4                    |

| 2  | Virtual Battery<br>Switch                                                                                                  | 1-2 (UP) – normal operation Virtual Battery switch is pulled high (disabled). The system acts as if it is running on AC power | 2-3 (DOWN) – Virtual<br>Battery switch is pulled<br>low. This enables the<br>virtual battery and the<br>system acts as if it is<br>running from a battery<br>source | SW8A1 <sup>2</sup>      |

| 3  | Virtual Battery<br>Jumper                                                                                                  | 1-x (OUT) – normal<br>operation<br>Virtual battery status<br>is controlled by SW9A2                                           | 1-2 (IN) – Override<br>switch SW9A2 condition.<br>System will always act<br>as if it is running from a<br>battery source                                            | J8A1                    |

| 4  | Lid Jumper                                                                                                                 | 1-x (OUT) – normal 1-2 (IN) operation switch on circuit.                                                                      |                                                                                                                                                                     | J9A1                    |

| 5  | Lid Switch                                                                                                                 | 1-2 (UP) – normal<br>operation<br>LID switch is pulled<br>high                                                                | 2-3 (DOWN) – LID<br>switch is pulled low                                                                                                                            | SW9A1 <sup>2</sup>      |

| 6  | Clear RTC                                                                                                                  | 1-x (OUT) – normal operation                                                                                                  | 1-2 (IN) to clear CMOS                                                                                                                                              | J4H1                    |

| 7  | Force Shutdown                                                                                                             | No Stuff                                                                                                                      | Reserved                                                                                                                                                            | J7G1                    |

| 8a | BSEL0 Setting                                                                                                              | No Stuff                                                                                                                      | Reserved                                                                                                                                                            | J8G2                    |

| 8b | BSEL1 Setting                                                                                                              | 1-2 – Processor BSEL<br>Select                                                                                                | OUT - 400 MHz<br>OUT - 533 MHz                                                                                                                                      | J8G3                    |

| 8c | BSEL2 Setting                                                                                                              | 1-2 – Processor BSEL<br>Select                                                                                                | 2-3 - 400 MHz<br>OUT - 533 MHz                                                                                                                                      | J9G3                    |

| 9a | Manual VIDs:<br>VID 6 (1-2)<br>VID 5 (3-4)<br>VID 4 (5-6)<br>VID 3 (7-8)<br>VID 2 (9-10)<br>VID 1 (11-12)<br>VID 0 (13-14) | IN – normal operation<br>(1-2)<br>(3-4)<br>(5-6)<br>(7-8)<br>(9-10)<br>(11-12)<br>(13-14)                                     | OUT – Refer to<br>Section 4.5 and<br>Appendix B                                                                                                                     | J1B1                    |

| #   | Description                  | Default Setting <sup>1</sup> Optional Setting |                                                           | Reference<br>Designator |

|-----|------------------------------|-----------------------------------------------|-----------------------------------------------------------|-------------------------|

| 9b  | VID CPU Override4<br>(15-16) | OUT – normal<br>operation                     | 15-16 (IN) – Override to<br>allow manual VID<br>operation | J1B1                    |

| 10a | CFG0 Setting                 | Refer to 9                                    | J6F1                                                      |                         |

| 10b | CFG1 Setting                 | Refer to <u>s</u>                             | J7F2                                                      |                         |

| 11  | Reserved                     | OUT – normal operation Reserved               |                                                           | J7F1                    |

| 12  | PS_ON#                       | 1-2 – normal operation                        | 2-3 - Reserved                                            | J7H4                    |

| 13  | 5V FET Load<br>Disable       | 1-X (OUT) load 1-2 (IN) no load               |                                                           | J4J1                    |

| 14  | 12V FET Load<br>Disable      | 1-2 (IN) no load                              | 1-X (OUT) load                                            | J5J2                    |

#### NOTES:

- 1. A jumper consists of two or more pins mounted on the motherboard. When a jumper cap is placed over two pins, it is designated as IN. When there are more than two pins on the jumper, the pins to be shorted are indicated as 1–2 (to short pin 1 to pin 2), 2–3 (to short pin 2 to pin 3), etc. When no jumper cap is to be placed on the jumper, it is designated as OUT.

- 2. When a switch is designated as 1–2, the switch slide is positioned such that pins 1 and 2 are shorted together.

- 3. H8 Jumper programming procedure is shown in <u>Section 4.9</u>.

*Note:* VID Override Jumper settings are shown in <u>Appendix B</u>.

User's Manual 31

# 4.4 BSEL Jumper Settings

The jumper settings in <u>Table 10</u> are provided to accommodate frequency selection for the processor. The CK-540 clock chip accepts two signals from the Intel® Atom $^{\text{TM}}$  processor.

**Table 10. BSEL Jumper Settings**

|                       |                                   | Proce                    | Intel® SCH                   |                          |

|-----------------------|-----------------------------------|--------------------------|------------------------------|--------------------------|

|                       |                                   | CPU                      | Override                     | Graphics                 |

|                       | Processor driven                  | J8G3 → 1-2<br>J9G3 → 1-2 | No override                  | See note.                |

| FSB<br>Speed<br>(MHz) | 400<br>(Host CLK = 100 MHz)       | J8G3→ Open<br>J9G3→ 2-3  | CPU BSEL 1=0<br>CPU BSEL 2=1 | J6F1 → 2-3<br>J7F2 → 2-3 |

|                       | Default  533 (Host CLK = 133 MHz) | J8G3→ Open<br>J9G3→ Open | CPU BSEL 1=0<br>CPU BSEL 2=0 | J6F1 → 1-2<br>J7F2 → 2-3 |

**NOTE:** Jumpers J7F2 and J6F1 must be set according to the FSB frequency to ensure 200-MHz operation.

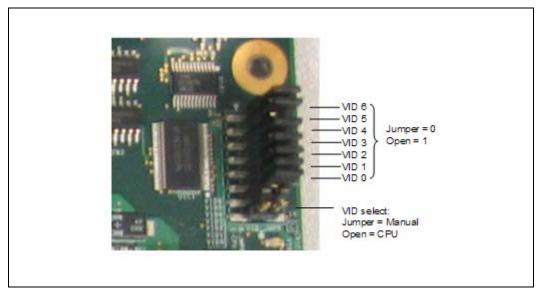

# 4.5 Manual VID Support for CPU

The Crown Beach supports manual VID operation for the processor VR. A header (J1B1) is provided to incorporate "VID override". VID override allows for overriding the CPU VID outputs to the CPU VCC\_CORE VR. The intent of the "VID override" circuit is to enable debugging and testing. See <a href="Appendix B">Appendix B</a> for the VID code table.

**Note:** When manually overriding the VID outputs, an open jumper position will result in logic '1' on the corresponding VID signal. Closing the jumper position will result in logic '0' on the corresponding VID signal.

User's Manual 32

Figure 6. Crown Beach Manual VID

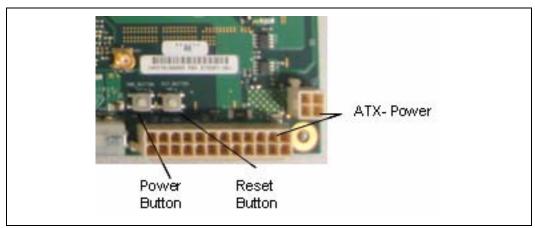

#### 4.6 Power On and Reset Push Buttons

The Crown Beach board has two pushbuttons, POWER and RESET. The POWER button releases power to the entire board causing the board to boot. The RESET button forces all systems to warm reset.

The two buttons are located near the ATX-Power connector. The POWER button is located at SW3J1 and the RESET button is located at SW2J1. See <u>Figure 7</u>.

Figure 7. Crown Beach Power On and Reset Buttons

User's Manual 33

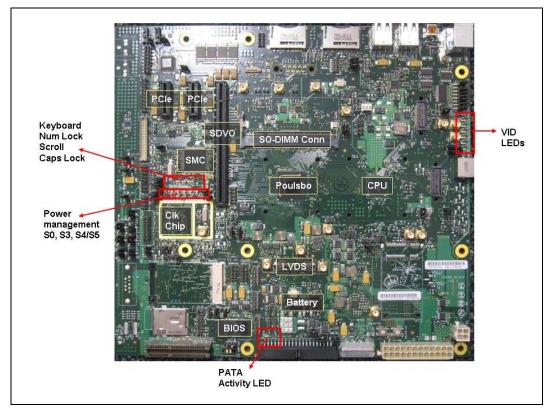

# 4.7 **LEDs**

$\underline{\text{Figure 8}}$  reveals the location of the LEDs and  $\underline{\text{Table 11}}$  describes the function of the LEDs and their reference designators

**Table 11. Crown Beach LEDs**

| #  | Function             | Reference Designator |

|----|----------------------|----------------------|

| 1  | Keyboard number lock | CR8E2                |

| 2  | Keyboard scroll lock | CR8E3                |

| 3  | Keyboard caps lock   | CR8E1                |

| 4  | System State S0      | CR8E7                |

| 5  | System State S3 Cold | CR7E1                |

| 6  | System State S4/S5   | CR8E5                |

| 7  | PATA Activity        | CR6J1                |

| 8  | VID Setting 0        | CR1C1                |

| 9  | VID Setting 1        | CR1C2                |

| 10 | VID Setting 2        | CR1D1                |

| 11 | VID Setting 3        | CR1D2                |

| 12 | VID Setting 4        | CR1D3                |

| 13 | VID Setting 5        | CR1D4                |

| 14 | VID Setting 6        | CR1D5                |

User's Manual 34

Figure 8. Crown Beach LEDs

# 4.8 PCI Express\* X1 Slots and Mini Card Connectors

# 4.8.1 Mini Card A connector (J7H1) is enabled by default

To enable PCI Express\* Slot 1 (J8C1) Mini Card A (J7H1) must be redirected to Slot 1.

Table 12. PCI Express\* Slot 1 Board Rework to Enable Functionality

| Rework        | Impacted components                                                                                                                | Comments                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Slot 1 | Remove – R6D1, R6D3, R6E2, R6E3,<br>R8F19, R8F21<br>Populate 0 Ohms – R6D2, R6D4,<br>R6E1, R6E4<br>Populate 33 Ohms - R8F22, R8F20 | Rework provides proper connectivity for PCI Express* Slot 1. Refer to the Mini Card A sheet of the Crown Beach Schematics and layout for details. |

User's Manual 35

## 4.8.2 Mini Card B connector (J2G1) is disabled by default

To enable the port for Mini Card B (J2G1), PCI Express\* Slot 0 (J7C1) and USB Port 0 (J2A1) devices must be redirected to the Mini Card B connector.

Table 13. Mini Card B Board Rework to Enable Functionality

| Rework             | Impacted components                               | Comments                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Mini Card B | Remove – R2B2, R2B4  Populate – R2B3, R2B5, R8Y7, | Rework provides proper USB and SIM card connectivity for wireless WAN cards from Sierra Wireless* and Option* only. However, there are a significant number of additional no-stuff components that must be populated for full functionality. Refer to the Mini Card B sheet of the Crown Beach Schematics for details.  USB Port 0 functionality through connector J2A1 is disabled when Mini Card B is enabled. |

# 4.9 H8S (JTAG) Programming Headers

The microcontroller firmware for system management/keyboard/mouse control can be upgraded in two ways:

- 1. By use of a special MS-DOS utility (in-circuit).

- 2. By use of an external computer connected (remotely) to the system through the serial port on the board.

## 4.9.1 H8 In-System Programming

If the user chooses in-system programming of the Crown Beach board, ensure that the following files are available on the DOS bootable media:

1. EC\_xx.bin - EC application

2. Fcntl.bin - Renesas Technology\* flash algorithm data file

3. Kscflash.exe - downloader

Boot to a DOS environment on the Crown Beach machine and type "kscflash ec\_xx.bin" to begin programming the EC.

## 4.9.2 H8 Remote Programming

If the user chooses to use an external computer (remote programming) connected to the system through the serial port, there are three jumpers that must be set correctly. Refer to <a href="Table 9">Table 9</a> for a summary of these jumpers and refer to the Crown Beach schematic for the location of each jumper.

The sequence of events necessary to program the H8 is as follows:

User's Manual 36

#### Reference Board Summary

- 1. Extract all files (keep them in the same folder) to a single directory of your choice on the host machine or on a floppy disk (recommended).

- 2. Connect a NULL modem cable to the serial ports of each platform (host and unit to be flashed).

- 3. With the board powered off, move the jumpers listed in <u>Table 14</u> to the programming stuffing option.

- 4. Attach an ATX power supply to the system and power up the board.

- 5. Boot the host system into a DOS environment using DOS bootable media

- 6. Install a serial port onto the target board header J9F1.

- 7. Hook up a null modem cable.

- 8. From the directory where you extracted the files on the host machine, run the "kscflash ec\_xx.bin /remote" command to program H8 through the serial port.

- 9. Follow the flash utility instructions.

- 10. With the board powered off, return the jumpers to their default settings.

**Note:** Make sure the board is not powered on, and the power supply is disconnected before moving any of the jumpers.

User's Manual 37

**Table 14. H8 Programming Jumpers**

| # | Jumper                                | Reference<br>Designator | Default Stuffing Option             | Programming Stuffing Option                                                  |  |  |

|---|---------------------------------------|-------------------------|-------------------------------------|------------------------------------------------------------------------------|--|--|

| 1 | Remote H8<br>Programming<br>(BB_PROG) | J8D4                    | 1-2 – normal operation<br>(Default) | 1-x – link the Host Unit to On Board H8 Remove Power Supply from the system. |  |  |

| 2 | Remote H8<br>Programming<br>(JTAG)    | J8E1<br>J8E4            | 1-X (Open)                          | 1-2 (Short) – to program H8                                                  |  |  |

## 4.10 UART Connector

§

User's Manual 38

# 5 Quick Start

The CRB is configured in a protective chassis. To access to the board with chassis open, use caution when configuring the hardware and observe proper safety cautions and warnings. The following sections summarize the necessary hardware and power-on instructions.

**Caution:** Always turn off the power and unplug the power cord before entering protective chassis. The user is required to observe extra precautions when handling and

operating the system.

**Note:** Review the document provided with the Development Kit titled *Important Safety and Regulatory Information*. This document contains addition safety warnings and cautions.

### 5.1 Required Peripherals

- DDR2 400- or 533-MHz SDRAM SO-DIMM

- ATX power supply

- Keyboard and mouse

- Hard drive

- Hard drive cable

- Graphics option

**Note:** PCI Express\* and ADD2N (VGA output provided) graphics card "Quick Start" options are not included in this document.

User's Manual 39

# 5.2 Graphics Assembly (LVDS Panel)

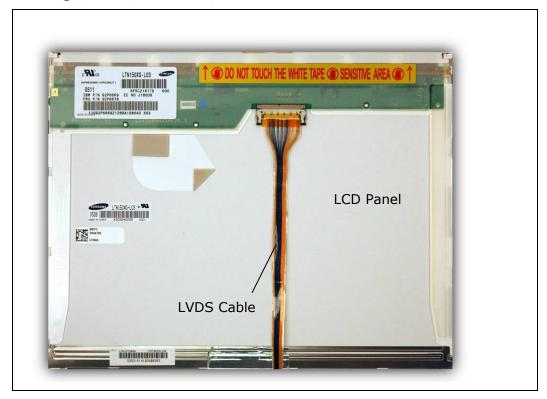

Figure 9. Samsung 15 inch (381.00 mm) Panel

User's Manual 40

Complete the following steps to operate the reference board with the Samsung 15 inch (381.00 mm),  $1024 \times 768$  (LTN150XG-L08) Panel. These steps will change if using different displays.

**Step 1**: Remove the Orange/Yellow tape from the Crown Beach Board.

Figure 10. Crown Beach Board

User's Manual 41

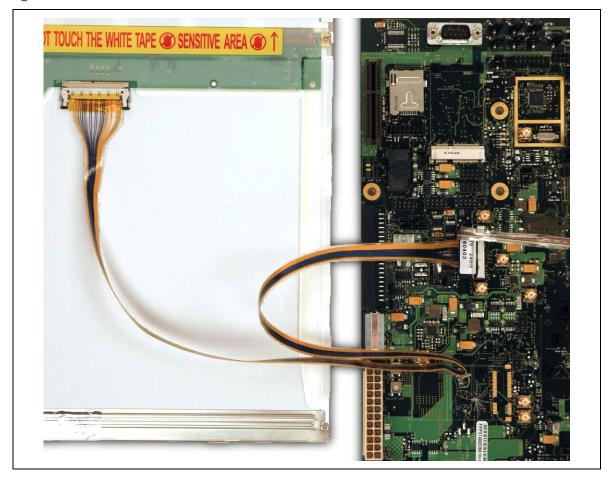

**Step 2**: Attach the LVDS cable to the Samsung panel and Crown Beach Board.

Figure 11. LVDS Cable Connected to the Crown Beach Board

User's Manual 42

Step 3: Connect the Back Light Inverter (BLI) to the Samsung panel and LVDS cable.

**Step 4**: In the Firmware Configuration Menu, go to: Chipset -> North Bridge Configuration -> Boot Display Configuration -> Flat Panel Type to 1024x768 Samsung 15 inch (381.00 mm).

### 5.3 Power Up

Complete the following steps to operate the reference board.

- 1. Place a DDR2 SO-DIMM in memory socket J6D1.

- 2. Install or verify the configuration jumpers as shown in <u>Section 4.3.1</u>.

- 3. Verify presence of RTC battery in Battery Holder at XBT5H1.

- 4. Plug in an ATX power supply into connectors J3J2 and J1J1; the connectors are keyed and will only fit in one position.

- 5. Connect a hard drive to connector J4J3 using a PATA cable (red stripe toward pin 1). Connect ATX power to hard drive.

- 6. Connect a PS/2 keyboard to connector J1A2 (bottom)

- 7. Connect a PS/2 mouse to connector J1A2 (top)

Note: You can reverse the connections of the keyboard and mouse.

- 8. If internal graphics are not used, plug a PCI Express\* Graphics card in the PCI-E x1 slot J7C1 and connect a monitor to the card.

User's Manual 43

Note: VGA output is provided by using the ADD2N card on the SDVO port.

The following steps are optional depending on the user's needs: