# 87C196CB Supplement to 8XC196NT User's Manual

# intel

ownload from Www.Somanuals.com. All Manuals Search And Download.

### 87C196CB Supplement to 8XC196NT User's Manual

August 2004

Order Number: 272787-003

Download from Www.Somanuals.com. All Manuals Search And Download.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 87C196CB and 8XC196NT microprocessors may contain design defects or errors known as errata which may cause the products to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998, 2004

\*Third-party brands and names are the property of their respective owners.

|       | PTER 1<br>JIDE TO THIS MANUAL                         |

|-------|-------------------------------------------------------|

| 1.1   | MANUAL CONTENTS 1-1                                   |

| 1.2   | RELATED DOCUMENTS 1-2                                 |

| AR    | PTER 2<br>CHITECTURAL OVERVIEW                        |

|       | DEVICE FEATURES                                       |

| 2.2   | BLOCK DIAGRAM                                         |

| 2.3   | INTERNAL TIMING                                       |

|       | PTER 3<br>MORY PARTITIONS                             |

| 3.1   | MEMORY MAP, SPECIAL-FUNCTION REGISTERS, AND WINDOWING |

| -     | PTER 4<br>ANDARD AND PTS INTERRUPTS                   |

| 4.1   | INTERRUPT SOURCES, VECTORS, AND PRIORITIES 4-1        |

| -     | PTER 5<br>PORTS                                       |

| 5.1   | PORT 0 AND EPORT                                      |

|       | PTER 6<br>IALOG-TO-DIGITAL (A/D) CONVERTER            |

|       | ADDITIONAL A/D INPUT CHANNELS                         |

|       | PTER 7<br>IN SERIAL COMMUNICATIONS CONTROLLER         |

| 7.1   | CAN FUNCTIONAL OVERVIEW                               |

| 7.2   | CAN CONTROLLER SIGNALS AND REGISTERS                  |

| 7.3   | CAN CONTROLLER OPERATION                              |

| 7.3.′ | 1 Address Map7-5                                      |

| 7.3.2 | 2 Message Objects                                     |

|       | 8.2.1 Receive and Transmit Priorities7-6              |

|       | 8.2.2 Message Acceptance Filtering7-6                 |

| 7.3.3 |                                                       |

| 7.3.4 | 4 Error Detection and Management Logic7-9             |

| 7.3.5 |                                                       |

|       | B.5.1   Bit Timing Equations                          |

| 7.4   | CONFIGURING THE CAN CONTROLLER                        |

| 7.4.′ |                                                       |

| 7.4.2 |                                                       |

| 7.4.3 | Programming the Bit Timing 1 (CAN_BTIME1) Register    |

| 7.4.4        | Programming a Message Acceptance Filter7-           | 17        |

|--------------|-----------------------------------------------------|-----------|

| 7.5          | CONFIGURING MESSAGE OBJECTS                         | 20        |

| 7.5.1        | Specifying a Message Object's Configuration7-2      | 21        |

| 7.5.2        | Programming the Message Object Identifier7-2        | 22        |

| 7.5.3        | Programming the Message Object Control Registers7-2 | 23        |

| 7.5.3        |                                                     |           |

| 7.5.3        |                                                     |           |

| 7.5.4        | Programming the Message Object Data7-2              | 23        |

| 7.6          | ENABLING THE CAN INTERRUPTS                         | <u>29</u> |

| 7.7          | DETERMINING THE CAN CONTROLLER'S INTERRUPT STATUS   | 32        |

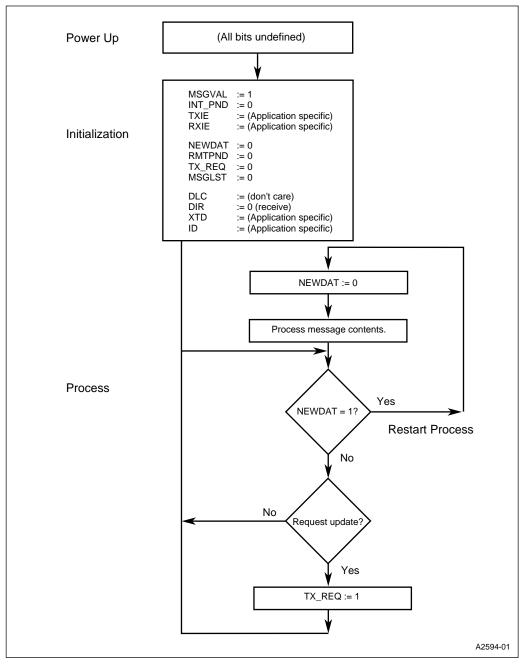

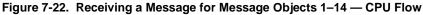

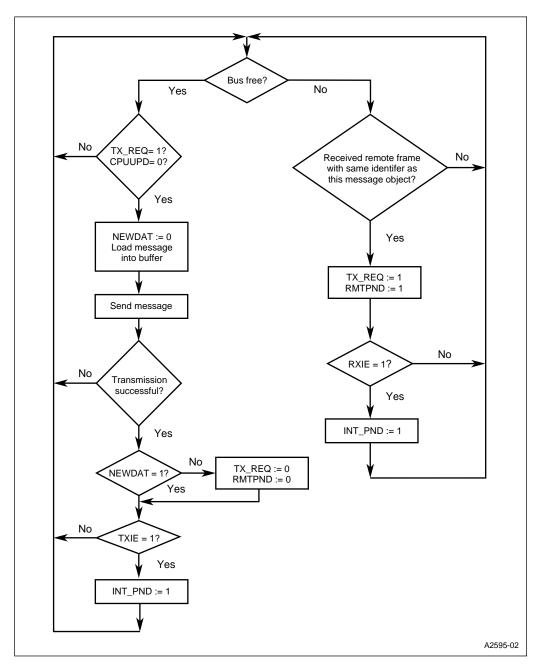

| 7.8          | FLOW DIAGRAMS                                       | 35        |

| 7.9          | DESIGN CONSIDERATIONS                               | 41        |

| 7.9.1        | Hardware Reset7-4                                   | 41        |

| 7.9.2        | Software Initialization7-4                          |           |

| 7.9.3        | Bus-off State7-4                                    | 41        |

| CHAPT<br>SPE | FER 8<br>ECIAL OPERATING MODES                      |           |

| 8.1          | CLOCK CIRCUITRY                                     | -1        |

#### **CHAPTER 9**

#### INTERFACING WITH EXTERNAL MEMORY

| 9.1 | ADDRESS PINS     | 9-1 |  |

|-----|------------------|-----|--|

| 9.2 | BUS TIMING MODES | 9-1 |  |

#### **CHAPTER 10**

#### PROGRAMMING THE NONVOLATILE MEMORY

| 10.1   | SIGNATURE WORD AND PROGRAMMING VOLTAGES     |      |

|--------|---------------------------------------------|------|

| 10.2   | MEMORY MAP FOR SLAVE PROGRAMMING MODE       | 10-1 |

| 10.3   | MEMORY MAP AND CIRCUIT FOR AUTO PROGRAMMING | 10-2 |

| 10.4   | MEMORY MAP FOR SERIAL PORT PROGRAMMING      | 10-3 |

| 10.4.1 | Selecting Bank 0 (FF2000–FF7FFFH)           | 10-4 |

| 10.4.2 | 2 Selecting Bank 1 (FF8000–FFFFFFH)         | 10-4 |

#### APPENDIX A

#### SIGNAL DESCRIPTIONS

| A.1 | FUNCTIONAL GROUPINGS OF SIGNALS | A-1          |

|-----|---------------------------------|--------------|

| A.2 | SIGNAL DESCRIPTIONS             | A-3          |

| A.3 | DEFAULT CONDITIONS              | <b>\-1</b> 4 |

#### GLOSSARY

#### INDEX

### FIGURES

| Figure       |                                                                                                                                        | Page         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

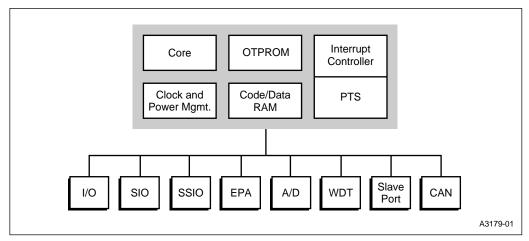

| 2-1          | 87C196CB Block Diagram                                                                                                                 | 2-2          |

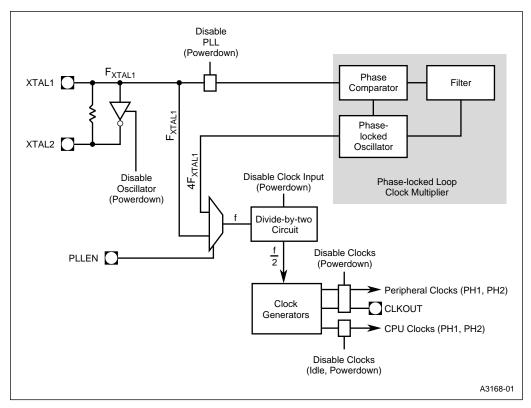

| 2-2          | Clock Circuitry                                                                                                                        |              |

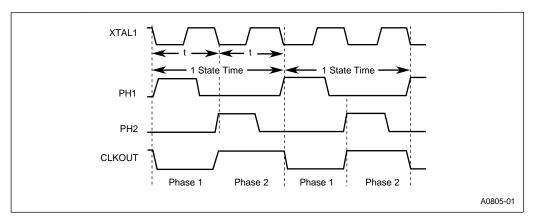

| 2-3          | Internal Clock Phases                                                                                                                  |              |

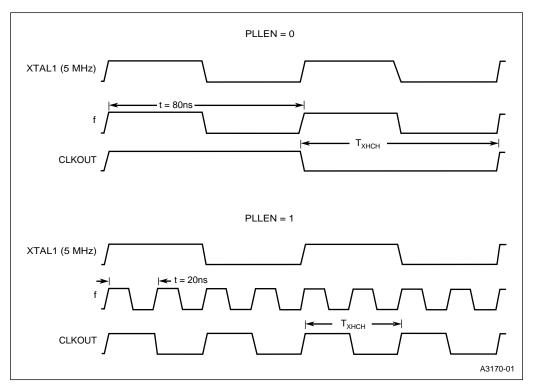

| 2-4          | Effect of Clock Mode on CLKOUT Frequency                                                                                               |              |

| 4-1          | Interrupt Mask 1 (INT_MASK1) Register                                                                                                  |              |

| 4-2          | interrupt Pending 1 (INT_PEND1) Register                                                                                               | 4-2          |

| 5-1          | Port x Pin Input (Px_PIN) Register                                                                                                     | 5-1          |

| 5-2          | Extended Port I/O Direction (EP_DIR) Register                                                                                          |              |

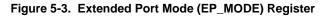

| 5-3          | Extended Port Mode (EP_MODE) Register                                                                                                  |              |

| 5-4          | Extended Port Input (EP_PIN) Register                                                                                                  | 5-3          |

| 5-5          | Extended Port Data Output (EP_REG) Register                                                                                            | 5-3          |

| 6-1          | A/D Command (AD_COMMAND) Register                                                                                                      |              |

| 6-2          | A/D Result (AD_RESULT) Register — Read Format                                                                                          |              |

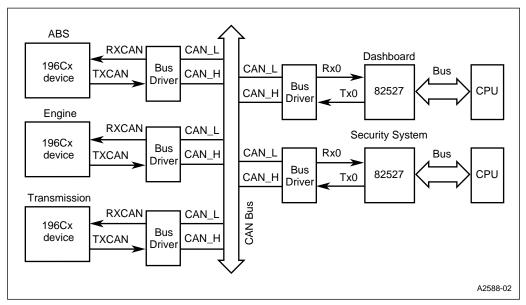

| 7-1          | A System Using CAN Controllers                                                                                                         |              |

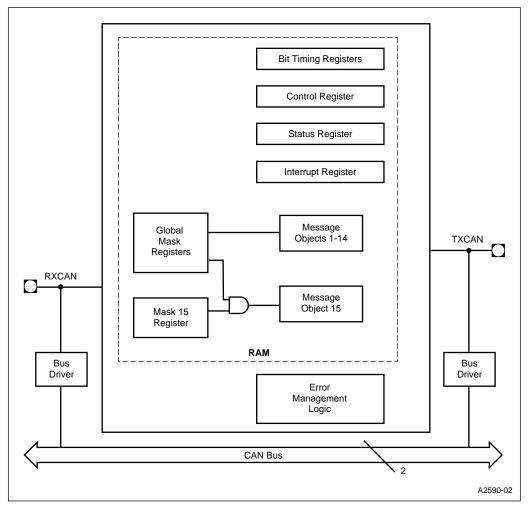

| 7-2          | CAN Controller Block Diagram                                                                                                           |              |

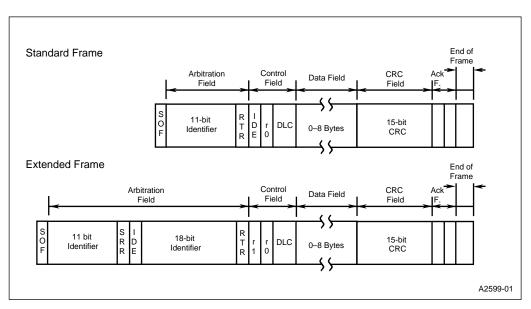

| 7-3          | CAN Message Frames                                                                                                                     |              |

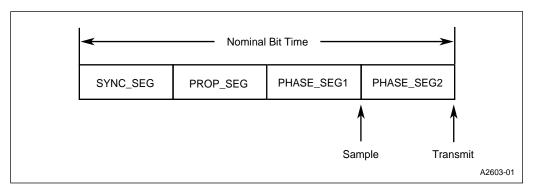

| 7-4          | A Bit Time as Specified by the CAN Protocol                                                                                            |              |

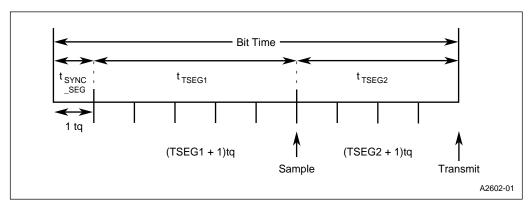

| 7-5          | A Bit Time as Implemented in the CAN Controller                                                                                        |              |

| 7-6          | CAN Control (CAN_CON) Register                                                                                                         |              |

| 7-7          | CAN Bit Timing 0 (CAN_BTIME0) Register                                                                                                 |              |

| 7-8          | CAN Bit Timing 1 (CAN_BTIME1) Register                                                                                                 |              |

| 7-9          | CAN Standard Global Mask (CAN_SGMSK) Register                                                                                          |              |

| 7-10         | CAN Extended Global Mask (CAN_EGMSK) Register                                                                                          |              |

| 7-11         | CAN Message 15 Mask (CAN_MSK15) Register                                                                                               |              |

| 7-12         | CAN Message Object <i>x</i> Configuration (CAN_MSGxCFG) Register                                                                       |              |

| 7-13         | CAN Message Object <i>x</i> Identifier (CAN_MSG <i>x</i> ID0–3) Register                                                               |              |

| 7-14         | CAN Message Object <i>x</i> Control 0 (CAN_MSGxCON0) Register                                                                          |              |

| 7-15         | CAN Message Object <i>x</i> Control 1 (CAN_MSG <i>x</i> CON1) Register<br>CAN Message Object Data (CAN_MSG <i>x</i> DATA0–7) Registers |              |

| 7-16<br>7-17 | CAN Message Object Data (CAN_MSGXDATA0-7) Registers                                                                                    |              |

| 7-17         | CAN Control (CAN_CON) Register<br>CAN Message Object <i>x</i> Control 0 (CAN_MSGxCON0) Register                                        |              |

| 7-18         | CAN Interrupt Pending (CAN_INT) Register                                                                                               | 7-31<br>7_32 |

| 7-19         | CAN Status (CAN_STAT) Register                                                                                                         |              |

| 7-21         | CAN Message Object <i>x</i> Control 0 (CAN_MSG <i>x</i> CON0) Register                                                                 |              |

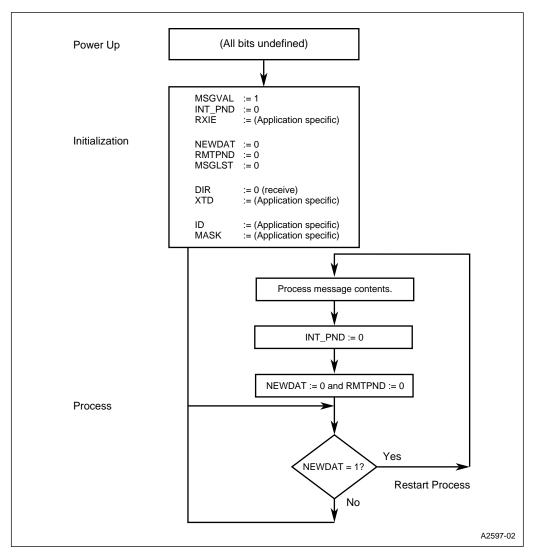

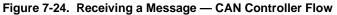

| 7-22         | Receiving a Message for Message Objects 1–14 — CPU Flow                                                                                |              |

| 7-23         | Receiving a Message for Message Object 15 — CPU Flow                                                                                   |              |

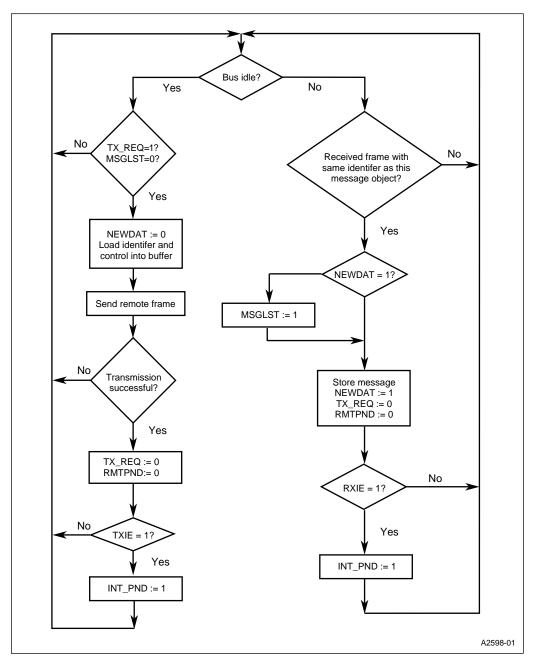

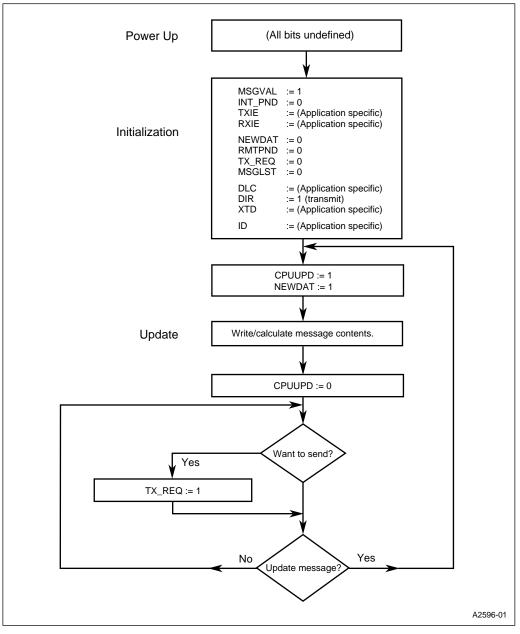

| 7-24         | Receiving a Message — CAN Controller Flow                                                                                              |              |

| 7-25         | Transmitting a Message — CPU Flow                                                                                                      |              |

| 7-26         | Transmitting a Message — CAN Controller Flow                                                                                           |              |

| 8-1          | Clock Circuitry                                                                                                                        |              |

| 9-1          | Modes 0 and 3 Timings                                                                                                                  |              |

| 9-2          | Chip Configuration 1 (CCR1) Register                                                                                                   |              |

| 10-1         | Auto Programming Circuit                                                                                                               |              |

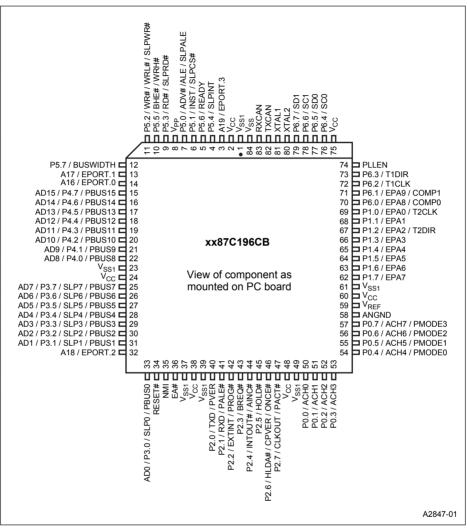

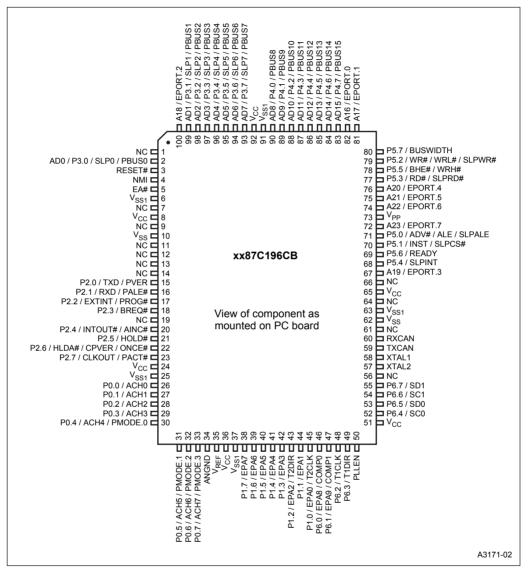

| A-1          | 87C196CB 84-pin PLCC Package                                                                                                           |              |

#### FIGURES

| Figure | F                            | Page  |

|--------|------------------------------|-------|

| A-2    | 87C196CB 100-pin QFP Package | . A-3 |

#### CONTENTS

### intel

### TABLES

| Table |                                                                          | Page |

|-------|--------------------------------------------------------------------------|------|

| 1-1   | Related Documents                                                        | 1-2  |

| 2-1   | Features of the 8XC196NT and 87C196CB                                    | 2-1  |

| 2-2   | State Times at Various Frequencies                                       | 2-4  |

| 2-3   | Relationships Between Input Frequency, Clock Multiplier, and State Times | 2-5  |

| 3-1   | Register File Memory Addresses                                           | 3-1  |

| 3-2   | 87C196CB Memory Map                                                      | 3-2  |

| 3-3   | 87C196CB Peripheral SFRs                                                 | 3-3  |

| 3-4   | CAN Peripheral SFRs                                                      |      |

| 3-5   | Selecting a Window of Peripheral SFRs                                    |      |

| 3-6   | Selecting a Window of the Upper Register File                            |      |

| 3-7   | Selecting a Window of Upper Register RAM                                 | 3-8  |

| 3-8   | Windows                                                                  | 3-9  |

| 3-9   | WSR Settings and Direct Addresses for Windowable SFRs                    | 3-11 |

| 4-1   | Interrupt Sources, Vectors, and Priorities                               | 4-1  |

| 5-1   | 87C196CB Input/Output Ports                                              | 5-1  |

| 6-1   | A/D Converter Pins                                                       | 6-1  |

| 7-1   | CAN Controller Signals                                                   | 7-3  |

| 7-2   | Control and Status Registers                                             | 7-3  |

| 7-3   | CAN Controller Address Map                                               | 7-5  |

| 7-4   | Message Object Structure                                                 | 7-6  |

| 7-5   | Effect of Masking on Message Identifiers                                 | 7-7  |

| 7-6   | Standard Message Frame                                                   |      |

| 7-7   | Extended Message Frame                                                   | 7-8  |

| 7-8   | CAN Protocol Bit Time Segments                                           | 7-10 |

| 7-9   | CAN Controller Bit Time Segments                                         | 7-11 |

| 7-10  | Bit Timing Relationships                                                 |      |

| 7-11  | Bit Timing Requirements for Synchronization                              |      |

| 7-12  | Control Register Bit-pair Interpretation                                 |      |

| 7-13  | Cross-reference for Register Bits Shown in Flowcharts                    |      |

| 7-14  | Register Values Following Reset                                          |      |

| 9-1   | Modes 0 and 3 Timing Comparisons                                         |      |

| 10-1  | Signature Word and Programming Voltages                                  |      |

| 10-2  | Slave Programming Mode Memory Map                                        |      |

| 10-3  | Auto Programming Memory Map                                              |      |

| 10-4  | Serial Port Programming Mode Memory Map                                  |      |

| A-1   | 87C196CB Signals Arranged by Functional Categories                       |      |

| A-2   | Description of Columns of Table A-3                                      |      |

| A-3   | Signal Descriptions                                                      |      |

| A-4   | Definition of Status Symbols                                             |      |

| A-5   | 87C196CB Pin Status                                                      | A-14 |

Download from Www.Somanuals.com. All Manuals Search And Download.

### **Guide to This Manual**

Dov load from Www.Somanuals.com. All Manuals Search And Download.

Download from Www.Somanuals.com. All Manuals Search And Download.

### CHAPTER 1 GUIDE TO THIS MANUAL

This document is a supplement to the 8XC196NT Microcontroller User's Manual. It describes the differences between the 87C196CB and the 8XC196NT. For information not found in this supplement, please consult the 8XC196NT Microcontroller User's Manual (order number 272317) or the 87C196CB datasheet (87C196CA/87C196CB 20 MHz Advanced 16-Bit CHMOS Microcontroller with Integrated CAN 2.0, order number 272405).

#### 1.1 MANUAL CONTENTS

This supplement contains several chapters, an appendix, a glossary, and an index. This chapter, Chapter 1, provides an overview of the supplement. This section summarizes the contents of the remaining chapters and appendixes. The remainder of this chapter provides references to related documentation.

**Chapter 2** — **Architectural Overview** — compares the features of the 87C196CB with those of the 8XC196NT and describes the 87C196CB's internal clock circuitry.

**Chapter 3** — **Memory Partitions** — describes the addressable memory space of the 84-pin and 100-pin 87C196CB, lists the peripheral special-function registers (SFRs), and provides tables of WSR values for windowing higher memory into the lower register file for direct access.

**Chapter 4** — **Standard and PTS Interrupts** — describes the additional interrupts for the CAN (controller area network) peripheral and the SFRs that support those interrupts.

**Chapter 5** — **I/O Ports** — describes the port 0 and EPORT differences for the 100-pin 87C196CB. Both port 0 and the EPORT are implemented as eight-bit ports on the 100-pin 87C196CB, but as four-bit ports (like the 8XC196NT) on the 84-pin 87C196CB.

**Chapter 6** — **Analog-to-digital (A/D) Converter** — illustrates the SFRs that are affected by the implementation of port 0 as an eight-bit port.

**Chapter 7** — **CAN Serial Communications Controller** — describes the 87C196CB's integrated CAN controller and explains how to configure it. This integrated peripheral is similar to Intel's standalone 82527 CAN serial communications controller, supporting both the standard and extended message frames specified by the CAN 2.0 protocol parts A and B.

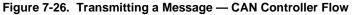

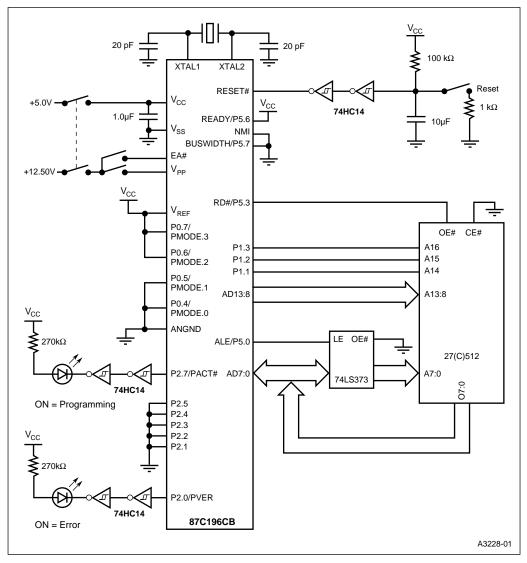

**Chapter 8** — **Special Operating Modes** — illustrates the clock control circuitry of the 87C196CB.

**Chapter 9** — **Interfacing with External Memory** — discusses differences in the bus timing modes supported by the 8XC196NT and the 87C196CB.

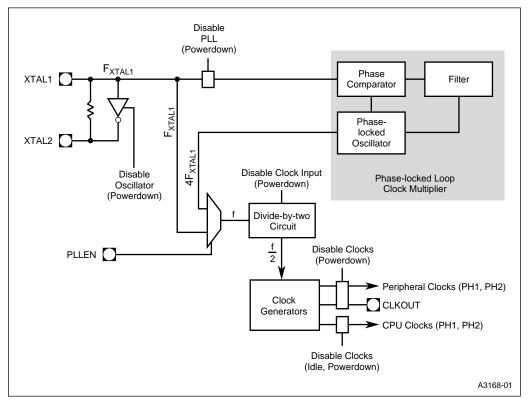

**Chapter 10** — **Programming the Nonvolatile Memory** — describes the memory maps and recommended circuits to support programming of the 87C196CB's 56 Kbytes of OTPROM.

**Appendix A** — **Signal Descriptions** — describes the additional signals implemented on the 87C196CB.

Glossary — defines terms with special meaning used throughout this supplement.

Index — lists key topics with page number references.

#### 1.2 RELATED DOCUMENTS

Table 1-1 lists additional documents that you may find useful in designing systems incorporating the 87C196CB microcontroller.

| Title and Description                                                                        | Order Number |

|----------------------------------------------------------------------------------------------|--------------|

| 8XC196NT Microcontroller User's Manual                                                       | 272317       |

| Automotive Products handbook                                                                 | 231792       |

| 87C196CB 20 MHz Advanced 16-Bit CHMOS Microcontroller with<br>Integrated CAN 2.0 (datasheet) | 272405       |

2

### Architectural Overview

Dov load from Www.Somanuals.com. All Manuals Search And Download.

Download from Www.Somanuals.com. All Manuals Search And Download.

### CHAPTER 2 ARCHITECTURAL OVERVIEW

This chapter describes architectural differences between the 87C196CB and the 8XC196NT. Both the 8XC196NT and the 87C196CB are designed for high-speed calculations and fast I/O. With the addition of the CAN (controller area network) peripheral, the 87C196CB reduces point-to-point wiring requirements, making it well-suited to automotive and factory automation applications.

The 87C196CB is available in either an 84-pin or a 100-pin package. The 84-pin 87C196CB, like the 8XC196NT, has up to 20 external address lines, enabling access to 1 Mbyte of linear address space. The 100-pin 87C196CB has four additional pins available for external address lines. With all 24 external address lines connected, the 100-pin 87C196CB can access 16 Mbytes of linear address space.

#### 2.1 DEVICE FEATURES

Table 2-1 lists the features of the 8XC196NT and the 87C196CB. The 87C196CB implements more OTPROM, more register RAM, four additional A/D channels, and the CAN peripheral. The 100-pin 87C196CB also implements four additional EPORT pins.

| Device   | Pins | отрком    | Register RAM † | Code/Data RAM<br>(bytes) | l/O Pins | EPA Pins | SIO/SSIO Ports | A/D Channels | External<br>Interrupt Pins | EPORT Pins | CAN Pins |

|----------|------|-----------|----------------|--------------------------|----------|----------|----------------|--------------|----------------------------|------------|----------|

| 8XC196NT | 68   | 0 or 32 K | 1 K            | 512                      | 56       | 10       | 2              | 4            | 1                          | 4          | 0        |

| 87C196CB | 84   | 56 K      | 1.5 K          | 512                      | 56       | 10       | 2              | 8            | 1                          | 4          | 2        |

| 87C196CB | 100  | 56 K      | 1.5 K          | 512                      | 60       | 10       | 2              | 8            | 1                          | 8          | 2        |

Table 2-1. Features of the 8XC196NT and 87C196CB

<sup>†</sup> Register RAM amount includes the 24 bytes allocated to the core SFRs and stack pointer.

#### 2.2 BLOCK DIAGRAM

Figure 2-1 shows the major blocks within the device. The 8XC196NT and 87C196CB have the same peripheral set with the exception of the CAN (controller area network) peripheral, which is unique to the 87C196CB. The CAN peripheral manages communications between multiple network nodes. This integrated peripheral is similar to Intel's standalone 82527 CAN serial communications controller, supporting both the standard and extended message frames specified by the CAN 2.0 protocol parts A and B.

Figure 2-1. 87C196CB Block Diagram

#### 2.3 INTERNAL TIMING

The 87C196CB's clock circuitry (Figure 2-2) implements phase-locked loop and clock multiplier circuitry, which can substantially increase the CPU clock rate while using a lower-frequency input clock. The clock circuitry accepts an input clock signal on XTAL1 provided by an external crystal or oscillator. Depending on the value of the PLLEN pin, this frequency is routed either through the phase-locked loop and multiplier or directly to the divide-by-two circuit. The multiplier circuitry can quadruple the input frequency ( $F_{XTAL1}$ ) before the frequency (f) reaches the divide-by-two circuit. The clock generators accept the divided input frequency (f/2) from the divide-by-two circuit and produce two nonoverlapping internal timing signals, PH1 and PH2. These signals are active when high.

#### NOTE

This manual uses lowercase "f" to represent the internal clock frequency. For the 87C196CB, f is equal to either  $F_{XTAL1}$  or  $4F_{XTAL1}$ , depending on the clock multiplier mode, which is controlled by the PLLEN input pin.

Figure 2-2. Clock Circuitry

The rising edges of PH1 and PH2 generate the internal CLKOUT signal (Figure 2-3). The clock circuitry routes separate internal clock signals to the CPU and the peripherals to provide flexibility in power management. It also outputs the CLKOUT signal on the CLKOUT pin. Because of the complex logic in the clock circuitry, the signal on the CLKOUT pin is a delayed version of the internal CLKOUT signal. This delay varies with temperature and voltage.

## intəl®

Figure 2-3. Internal Clock Phases

The combined period of phase 1 and phase 2 of the internal CLKOUT signal defines the basic time unit known as a *state time* or *state*. Table 2-2 lists state time durations at various frequencies.

| f<br>(Frequency Input to the<br>Divide-by-two Circuit) | State Time |

|--------------------------------------------------------|------------|

| 8 MHz                                                  | 250 ns     |

| 12 MHz                                                 | 167 ns     |

| 16 MHz                                                 | 125 ns     |

| 20 MHz                                                 | 100 ns     |

| Table 2-2. | State | Times | at | Various | Frequencies |

|------------|-------|-------|----|---------|-------------|

|------------|-------|-------|----|---------|-------------|

The following formulas calculate the frequency of PH1 and PH2, the duration of a state time, and the duration of a clock period (t).

PH1 (in MHz) =

$$\frac{f}{2}$$

= PH2 State Time (in µs) =  $\frac{2}{f}$  t =  $\frac{1}{f}$

Because the device can operate at many frequencies, this manual defines time requirements (such as instruction execution times) in terms of state times rather than specific measurements. Datasheets list AC characteristics in terms of clock periods (t; sometimes called  $T_{osc}$ ).

Figure 2-4 illustrates the timing relationships between the input frequency ( $F_{XTAL1}$ ), the operating frequency (f), and the CLKOUT signal with each PLLEN pin configuration. Table 2-3 details the relationships between the input frequency ( $F_{XTAL1}$ ), the PLLEN pin, the operating frequency (f), the clock period (t), and state times.

Figure 2-4. Effect of Clock Mode on CLKOUT Frequency

| Table 2-3. | Relationship | s Between I | nput Frequency, | Clock Mult | iplier, and | State Times |

|------------|--------------|-------------|-----------------|------------|-------------|-------------|

|            |              |             |                 |            |             |             |

| F <sub>XTAL1</sub><br>(Frequency<br>on XTAL1) | PLLEN | Multiplier | f<br>(Input Frequency to<br>the Divide-by-two Circuit) | t<br>(Clock<br>Period) | State Time |

|-----------------------------------------------|-------|------------|--------------------------------------------------------|------------------------|------------|

| 4 MHz                                         | 0     | 1          | 4 MHz                                                  | 250 ns                 | 500 ns     |

| 5 MHz                                         | 0     | 1          | 5 MHz                                                  | 200 ns                 | 400 ns     |

| 8 MHz                                         | 0     | 1          | 8 MHz                                                  | 125 ns                 | 250 ns     |

| 12 MHz                                        | 0     | 1          | 12 MHz                                                 | 83.5 ns                | 167 ns     |

| 16 MHz                                        | 0     | 1          | 16 MHz                                                 | 62.5 ns                | 125 ns     |

| 20 MHz                                        | 0     | 1          | 20 MHz                                                 | 50 ns                  | 100 ns     |

| 4 MHz                                         | 1     | 4          | 16 MHz                                                 | 62.5 ns                | 125 ns     |

| 5 MHz                                         | 1     | 4          | 20 MHz                                                 | 50 ns                  | 100 ns     |

Download from Www.Somanuals.com. All Manuals Search And Download.

## **Memory Partitions**

Dov load from Www.Somanuals.com. All Manuals Search And Download.

Download from Www.Somanuals.com. All Manuals Search And Download.

### CHAPTER 3 MEMORY PARTITIONS

This chapter describes the differences in the address space of the 87C196CB from that of the 8XC196NT. The 87C196CB has 56 Kbytes of one-time-programmable read-only memory (OT-PROM), while the 8XC196NT is available with 32 Kbytes. The 87C196CB also has an additional 512 bytes of register RAM.

The 87C196CB is available in either an 84-pin or a 100-pin package. The 84-pin 87C196CB, like the 8XC196NT, has up to 20 external address lines, enabling access to 1 Mbyte of linear address space. The 100-pin 87C196CB has four additional pins available for external address lines. With all 24 external address lines connected (A23:16 and AD15:0), the 100-pin 87C196CB can access 16 Mbytes of linear address space.

#### 3.1 MEMORY MAP, SPECIAL-FUNCTION REGISTERS, AND WINDOWING

Table 3-1 compares the register file addresses of the 8XC196NT and 87C196CB. Table 3-2 is a memory map of the 87C196CB. Table 3-3 lists the 87C196CB's peripheral SFRs (these are the same as those of the 8XC196NT). Table 3-4 lists the CAN peripheral SFRs, which are unique to the 87C196CB. Tables 3-5 through 3-9 provide the information necessary to window higher memory into the lower register file for direct access.

|              | e and Hex<br>ss Range | Description                         | Addressing Modes                      |  |  |

|--------------|-----------------------|-------------------------------------|---------------------------------------|--|--|

| СВ           | NT                    |                                     | _                                     |  |  |

| 1DFF<br>1C00 | _                     | Register RAM                        | Indirect, indexed, or windowed direct |  |  |

| 03FF<br>0100 | 03FF<br>0100          | Upper register file (register RAM)  | Indirect, indexed, or windowed direct |  |  |

| 00FF<br>001A | 00FF<br>001A          | Lower register file (register RAM)  | Direct, indirect, or indexed          |  |  |

| 0019<br>0018 | 0019<br>0018          | Lower register file (stack pointer) | Direct, indirect, or indexed          |  |  |

| 0017<br>0000 | 0017<br>0000          | Lower register file (CPU SFRs)      | Direct, indirect, or indexed          |  |  |

| Table 3-1. | Register F | ile Memory | Addresses |

|------------|------------|------------|-----------|

|------------|------------|------------|-----------|

| Hex<br>Address   | Description                                                                                         | Addressing Modes                             |

|------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------|

| FFFFFF<br>FF2080 | Program memory (After a device reset, the first instruction fetch is from FF2080H) $^{\dagger}$     | Indirect, indexed, extended                  |

| FF207F<br>FF2000 | Special purpose memory $^\dagger$                                                                   | Indirect, indexed, extended                  |

| FF1FFF<br>FF0600 | External device (memory or I/O) connected to address/data bus                                       | Indirect, indexed, extended                  |

| FF05FF<br>FF0400 | Internal code and data RAM<br>(mapped identically into pages FFH and 00H)                           | Indirect, indexed, extended                  |

| FF03FF<br>FF0100 | External device (memory or I/O) connected to address/data bus                                       | Indirect, indexed, extended                  |

| FF00FF<br>FF0000 | Reserved <sup>††</sup>                                                                              | Indirect, indexed, extended                  |

| FEFFFF<br>0F0000 | 100-pin 87C196CB: External device (memory or I/O)<br>84-pin 87C196CB: Overlaid memory <sup>††</sup> | Indirect, indexed, extended                  |

| 0EFFFF<br>010000 | External device (memory or I/O) connected to address/data bus                                       | Indirect, indexed, extended                  |

| 00FFFF<br>002000 | External device or remapped OTPROM ***                                                              | Indirect, indexed, extended                  |

| 001FFF<br>001FE0 | Memory-mapped SFRs                                                                                  | Indirect, indexed, extended                  |

| 001FDF<br>001F00 | Peripheral SFRs                                                                                     | Indirect, indexed, extended, windowed direct |

| 001EFF<br>001E00 | CAN SFRs                                                                                            | Indirect, indexed, extended                  |

| 001DFF<br>001C00 | Internal register RAM                                                                               | Indirect, indexed,<br>windowed direct        |

| 001BFF<br>000600 | External device (memory or I/O) connected to address/data bus; future SFR expansion                 | Indirect, indexed, extended                  |

| 0005FF<br>000400 | Internal code and data RAM<br>(mapped identically into pages 00H and FFH)                           | Indirect, indexed, extended                  |

| 0003FF<br>000100 | Upper register file (register RAM)                                                                  | Indirect, indexed,<br>windowed direct        |

| 0000FF<br>000000 | Lower register file (register RAM, stack pointer, CPU SFRs)                                         | Direct, indirect, indexed                    |

| Table 3-2. | 87C196CB | <b>Memory Map</b> |

|------------|----------|-------------------|

|------------|----------|-------------------|

<sup>†</sup> For the 87C196CB, the program and special-purpose memory locations (FF2000-FFFFFH) can reside either in external memory or in internal OTPROM.

<sup>††</sup> Locations xF0000-xF00FFH are reserved for in-circuit emulators. Do not use these locations except to initialize them. Except as otherwise noted, initialize unused program memory locations and reserved memory locations to FFH.

tit These locations can be either external memory (CCB2.2=0) or a copy of the OTPROM (CCB2.2=1).

|                    | Ports 0, 1, 2, and | 6 SFRs          |

|--------------------|--------------------|-----------------|

| Address            | High (Odd) Byte    | Low (Even) Byte |

| 1FDEH              | Reserved           | Reserved        |

| 1FDCH              | Reserved           | Reserved        |

| 1FDAH              | Reserved           | P0_PIN          |

| 1FD8H              | Reserved           | Reserved        |

| 1FD6H              | P6_PIN             | P1_PIN          |

| 1FD4H              | P6_REG             | P1_REG          |

| 1FD2H              | P6_DIR             | P1_DIR          |

| 1FD0H              | P6_MODE            | P1_MODE         |

| 1FCEH              | P2_PIN             | Reserved        |

| 1FCCH              | P2_REG             | Reserved        |

| 1FCAH              | P2_DIR             | Reserved        |

| 1FC8H              | P2_MODE            | Reserved        |

| 1FC6H              | Reserved           | Reserved        |

| 1FC4H              | Reserved           | Reserved        |

| 1FC2H              | Reserved           | Reserved        |

| 1FC0H              | Reserved           | Reserved        |

|                    | SIO and SSIO S     | SFRs            |

| Address            | High (Odd) Byte    | Low (Even) Byte |

| 1FBEH              | Reserved           | Reserved        |

| 1FBCH              | SP_BAUD (H)        | SP_BAUD (L)     |

| 1FBAH              | SP_CON             | SBUF_TX         |

| 1FB8H              | SP_STATUS          | SBUF_RX         |

| 1FB6H              | Reserved           | Reserved        |

| 1FB4H              | Reserved           | SSIO_BAUD       |

| 1FB2H              | SSIO1_CON          | SSIO1_BUF       |

| 1FB0H              | SSIO0_CON          | SSIO0_BUF       |

|                    | A/D SFRs           |                 |

| Address            | High (Odd) Byte    | Low (Even) Byte |

| 1FAEH              | AD_TIME            | AD_TEST         |

| 1FACH              | Reserved           | AD_COMMAND      |

| 1FAAH              | AD_RESULT (H)      | AD_RESULT (L)   |

|                    | EPA Interrupt \$   | SFRs            |

| Address            | High (Odd) Byte    | Low (Even) Byte |

| 1FA8H              | Reserved           | EPAIPV          |

| 1FA6H              | Reserved           | EPA_PEND1       |

| 1FA4H              | Reserved           | EPA_MASK1       |

| <sup>†</sup> 1FA2H | EPA_PEND (H)       | EPA_PEND (L)    |

| <sup>†</sup> 1FA0H | EPA_MASK (H)       | EPA_MASK (L)    |

| Table 3-3. 87C196CB Peripheral SFRs |

|-------------------------------------|

|-------------------------------------|

| Timer 1, Timer 2, and EPA SFRs |                 |                 |  |

|--------------------------------|-----------------|-----------------|--|

| Address                        | High (Odd) Byte | Low (Even) Byte |  |

| <sup>†</sup> 1F9EH             | TIMER2 (H)      | TIMER2 (L)      |  |

| 1F9CH                          | Reserved        | T2CONTROL       |  |

| <sup>†</sup> 1F9AH             | TIMER1 (H)      | TIMER1 (L)      |  |

| 1F98H                          | Reserved        | T1CONTROL       |  |

| 1F96H                          | Reserved        | Reserved        |  |

| 1F94H                          | Reserved        | Reserved        |  |

| 1F92H                          | Reserved        | Reserved        |  |

| 1F90H                          | Reserved        | Reserved        |  |

|                                | EPA SFRs        |                 |  |

| Address                        | High (Odd) Byte | Low (Even) Byte |  |

| <sup>†</sup> 1F8EH             | COMP1_TIME (H)  | COMP1_TIME (L)  |  |

| 1F8CH                          | Reserved        | COMP1_CON       |  |

| <sup>†</sup> 1F8AH             | COMP0_TIME (H)  | COMP0_TIME (L)  |  |

| 1F88H                          | Reserved        | COMP0_CON       |  |

| †1F86H                         | EPA9_TIME (H)   | EPA9_TIME (L)   |  |

| 1F84H                          | Reserved        | EPA9_CON        |  |

| †1F82H                         | EPA8_TIME (H)   | EPA8_TIME (L)   |  |

| 1F80H                          | Reserved        | EPA8_CON        |  |

| †1F7EH                         | EPA7_TIME (H)   | EPA7_TIME (L)   |  |

| 1F7CH                          | Reserved        | EPA7_CON        |  |

| †1F7AH                         | EPA6_TIME (H)   | EPA6_TIME (L)   |  |

| 1F78H                          | Reserved        | EPA6_CON        |  |

| †1F76H                         | EPA5_TIME (H)   | EPA5_TIME (L)   |  |

| 1F74H                          | Reserved        | EPA5_CON        |  |

| †1F72H                         | EPA4_TIME (H)   | EPA4_TIME (L)   |  |

| 1F70H                          | Reserved        | EPA4_CON        |  |

| <sup>†</sup> 1F6EH             | EPA3_TIME (H)   | EPA3_TIME (L)   |  |

| <sup>†</sup> 1F6CH             | EPA3_CON (H)    | EPA3_CON (L)    |  |

| †1F6AH                         | EPA2_TIME (H)   | EPA2_TIME (L)   |  |

| 1F68H                          | Reserved        | EPA2_CON        |  |

| †1F66H                         | EPA1_TIME (H)   | EPA1_TIME (L)   |  |

| †1F64H                         | EPA1_CON (H)    | EPA1_CON (L)    |  |

| †1F62H                         | EPA0_TIME (H)   | EPA0_TIME (L)   |  |

| 1F60H                          | Reserved        | EPA0_CON        |  |

<sup>†</sup> Must be addressed as a word.

|       |                 | Table 3-4. CAN  | - onprior |

|-------|-----------------|-----------------|-----------|

|       |                 |                 |           |

| Addr  | High (Odd) Byte | Low (Even) Byte | Addr      |

| 1EFEH | Reserved        | CAN_MSG15DATA7  | 1EBEH     |

| 1EFCH | CAN_MSG15DATA6  | CAN_MSG15DATA5  | 1EBCH     |

| 1EFAH | CAN_MSG15DATA4  | CAN_MSG15DATA3  | 1EBAH     |

| 1EF8H | CAN_MSG15DATA2  | CAN_MSG15DATA1  | 1EB8H     |

| 1EF6H | CAN_MSG15DATA0  | CAN_MSG15CFG    | 1EB6H     |

| 1EF4H | CAN_MSG15ID3    | CAN_MSG15ID2    | 1EB4H     |

| 1EF2H | CAN_MSG15ID1    | CAN_MSG15ID0    | 1EB2H     |

| 1EF0H | CAN_MSG15CON1   | CAN_MSG15CON0   | 1EB0H     |

|       | Message 1       | 4               |           |

| Addr  | High (Odd) Byte | Low (Even) Byte | Addr      |

| 1EEEH | Reserved        | CAN_MSG14DATA7  | 1EAEH     |

| 1EECH | CAN_MSG14DATA6  | CAN_MSG14DATA5  | 1EACH     |

| 1EEAH | CAN_MSG14DATA4  | CAN_MSG14DATA3  | 1EAAH     |

| 1EE8H | CAN_MSG14DATA2  | CAN_MSG14DATA1  | 1EA8H     |

| 1EE6H | CAN_MSG14DATA0  | CAN_MSG14CFG    | 1EA6H     |

| 1EE4H | CAN_MSG14ID3    | CAN_MSG14ID2    | 1EA4H     |

| 1EE2H | CAN_MSG14ID1    | CAN_MSG14ID0    | 1EA2H     |

| 1EE0H | CAN_MSG14CON1   | CAN_MSG14CON0   | 1EA0H     |

|       | Message 1       | 3               |           |

| Addr  | High (Odd) Byte | Low (Even) Byte | Addr      |

| 1EDEH | Reserved        | CAN_MSG13DATA7  | 1E9EH     |

| 1EDCH | CAN_MSG13DATA6  | CAN_MSG13DATA5  | 1E9CH     |

| 1EDAH | CAN_MSG13DATA4  | CAN_MSG13DATA3  | 1E9AH     |

| 1ED8H | CAN_MSG13DATA2  | CAN_MSG13DATA1  | 1E98H     |

| 1ED6H | CAN_MSG13DATA0  | CAN_MSG13CFG    | 1E96H     |

| 1ED4H | CAN_MSG13ID3    | CAN_MSG13ID2    | 1E94H     |

| 1ED2H | CAN_MSG13ID1    | CAN_MSG13ID0    | 1E92H     |

| 1ED0H | CAN_MSG13CON1   | CAN_MSG13CON0   | 1E90H     |

|       | Message 1       | 2               |           |

| Addr  | High (Odd) Byte | Low (Even) Byte | Addr      |

| 1ECEH | Reserved        | CAN_MSG12DATA7  | 1E8EH     |

| 1ECCH | CAN_MSG12DATA6  | CAN_MSG12DATA5  | 1E8CH     |

| 1ECAH | CAN_MSG12DATA4  | CAN_MSG12DATA3  | 1E8AH     |

| 1EC8H | CAN_MSG12DATA2  | CAN_MSG12DATA1  | 1E88H     |

| 1EC6H | CAN_MSG12DATA0  | CAN_MSG12CFG    | 1E86H     |

| 1EC4H | CAN_MSG12ID3    | CAN_MSG12ID2    | 1E84H     |

| 1EC2H | CAN_MSG12ID1    | CAN_MSG12ID0    | 1E82H     |

| 1EC0H | CAN_MSG12CON1   | CAN_MSG12CON0   | 1E80H     |

|       |                 |                 |           |

Table 3-4. CAN Peripheral SFRs

| Message 11     |                            |                            |  |

|----------------|----------------------------|----------------------------|--|

| Addr           | High (Odd) Byte            | Low (Even) Byte            |  |

| 1EBEH          | Reserved                   | CAN_MSG11DATA7             |  |

| 1EBCH          | CAN_MSG11DATA6             | CAN_MSG11DATA5             |  |

| 1EBAH          | CAN_MSG11DATA4             | CAN_MSG11DATA3             |  |

| 1EB8H          | CAN_MSG11DATA2             | CAN_MSG11DATA1             |  |

| 1EB6H          | CAN_MSG11DATA0             | CAN_MSG11CFG               |  |

| 1EB4H          | CAN_MSG11ID3               | CAN_MSG11ID2               |  |

| 1EB2H          | CAN_MSG11ID1               | CAN_MSG11ID0               |  |

| 1EB0H          | CAN_MSG11CON1              | CAN_MSG11CON0              |  |

|                | Message 1                  | 0                          |  |

| Addr           | High (Odd) Byte            | Low (Even) Byte            |  |

| 1EAEH          | Reserved                   | CAN_MSG10DATA7             |  |

| 1EACH          | CAN_MSG10DATA6             | CAN_MSG10DATA5             |  |

| 1EAAH          | CAN_MSG10DATA4             | CAN_MSG10DATA3             |  |

| 1EA8H          | CAN_MSG10DATA2             | CAN_MSG10DATA1             |  |

| 1EA6H          | CAN_MSG10DATA0             | CAN_MSG10CFG               |  |

| 1EA4H          | CAN_MSG10ID3               | CAN_MSG10ID2               |  |

| 1EA2H          | CAN_MSG10ID1               | CAN_MSG10ID0               |  |

| 1EA0H          | CAN_MSG10CON1              | CAN_MSG10CON0              |  |

|                | Message 9                  |                            |  |

| Addr           | High (Odd) Byte            | Low (Even) Byte            |  |

| 1E9EH          | Reserved                   | CAN_MSG9DATA7              |  |

| 1E9CH          | CAN_MSG9DATA6              | CAN_MSG9DATA5              |  |

| 1E9AH          | CAN_MSG9DATA4              | CAN_MSG9DATA3              |  |

| 1E98H          | CAN_MSG9DATA2              | CAN_MSG9DATA1              |  |

| 1E96H          | CAN_MSG9DATA0              | CAN_MSG9CFG                |  |

| 1E94H          | CAN_MSG9ID3                | CAN_MSG9ID2                |  |

| 1E92H          | CAN_MSG9ID1                | CAN_MSG9ID0                |  |

| 1E90H          | CAN_MSG9CON1               | CAN_MSG9CON0               |  |

|                | Message 8                  | 3                          |  |

| Addr           | High (Odd) Byte            | Low (Even) Byte            |  |

| 1E8EH          | Reserved                   | CAN_MSG8DATA7              |  |

| 1E8CH          | CAN_MSG8DATA6              | CAN_MSG8DATA5              |  |

| 1E8AH          | CAN_MSG8DATA4              | CAN_MSG8DATA3              |  |

| 1E88H          | CAN_MSG8DATA2              | CAN_MSG8DATA1              |  |

| 1E86H          | CAN_MSG8DATA0              | CAN_MSG8CFG                |  |

|                |                            | CAN MECSID2                |  |

| 1E84H          | CAN_MSG8ID3                | CAN_MSG8ID2                |  |

| 1E84H<br>1E82H | CAN_MSG8ID3<br>CAN_MSG8ID1 | CAN_MSG8ID2<br>CAN_MSG8ID0 |  |

| Table 3-4. CAN Peripheral SFRs (Continued) |                         |                 |                            |                             |                      |  |  |

|--------------------------------------------|-------------------------|-----------------|----------------------------|-----------------------------|----------------------|--|--|

|                                            | Message                 | 7               | Message 3 and Bit Timing 0 |                             |                      |  |  |

| Addr                                       | High (Odd) Byte         | Low (Even) Byte | Addr                       | Addr High (Odd) Byte Low (E |                      |  |  |

| 1E7EH                                      | Reserved                | CAN_MSG7DATA7   | 1E3EH                      | CAN_BTIME0 <sup>†</sup>     | CAN_MSG3DATA7        |  |  |

| 1E7CH                                      | CAN_MSG7DATA6           | CAN_MSG7DATA5   | 1E3CH CAN_MSG3DATA6        |                             | CAN_MSG3DATA5        |  |  |

| 1E7AH                                      | CAN_MSG7DATA4           | CAN_MSG7DATA3   | 1E3AH                      | CAN_MSG3DATA4               | CAN_MSG3DATA3        |  |  |

| 1E78H                                      | CAN_MSG7DATA2           | CAN_MSG7DATA1   | 1E38H                      |                             |                      |  |  |

| 1E76H                                      | CAN_MSG7DATA0           | CAN_MSG7CFG     | 1E36H                      | CAN_MSG3DATA0               | CAN_MSG3CFG          |  |  |

| 1E74H                                      | CAN_MSG7ID3             | CAN_MSG7ID2     | 1E34H                      | CAN_MSG3ID3                 | CAN_MSG3ID2          |  |  |

| 1E72H                                      | CAN_MSG7ID1             | CAN_MSG7ID0     | 1E32H                      | CAN_MSG3ID1                 | CAN_MSG3ID0          |  |  |

| 1E70H                                      | CAN_MSG7CON1            | CAN_MSG7CON0    | 1E30H                      | CAN_MSG3CON1                | CAN_MSG3CON0         |  |  |

|                                            | Message                 | 6               |                            | Message 2                   | 2                    |  |  |

| Addr                                       | High (Odd) Byte         | Low (Even) Byte | Addr                       | High (Odd) Byte             | Low (Even) Byte      |  |  |

| 1E6EH                                      | Reserved                | CAN_MSG6DATA7   | 1E2EH                      | Reserved                    | CAN_MSG2DATA7        |  |  |

| 1E6CH                                      | CAN_MSG6DATA6           | CAN_MSG6DATA5   | 1E2CH                      | CAN_MSG2DATA6               | CAN_MSG2DATA5        |  |  |

| 1E6AH                                      | CAN_MSG6DATA4           | CAN_MSG6DATA3   | 1E2AH                      | CAN_MSG2DATA4               | CAN_MSG2DATA3        |  |  |

| 1E68H                                      | CAN_MSG6DATA2           | CAN_MSG6DATA1   | 1E28H                      | CAN_MSG2DATA2               | CAN_MSG2DATA1        |  |  |

| 1E66H                                      | CAN_MSG6DATA0           | CAN_MSG6CFG     | 1E26H                      | CAN_MSG2DATA0               | CAN_MSG2CFG          |  |  |

| 1E64H                                      | CAN_MSG6ID3             | CAN_MSG6ID2     | 1E24H                      | CAN_MSG2ID3                 | CAN_MSG2ID2          |  |  |

| 1E62H                                      | CAN_MSG6ID1             | CAN_MSG6ID0     | 1E22H                      | CAN_MSG2ID1                 | CAN_MSG2ID0          |  |  |

| 1E60H                                      | CAN_MSG6CON1            | CAN_MSG6CON0    | 1E20H                      | CAN_MSG2CON1                | CAN_MSG2CON0         |  |  |

|                                            | Message 5 and In        | terrupts        | Message 1                  |                             |                      |  |  |

| Addr                                       | High (Odd) Byte         | Low (Even) Byte | Addr                       | High (Odd) Byte             | Low (Even) Byte      |  |  |

| 1E5EH                                      | CAN_INT                 | CAN_MSG5DATA7   | 1E1EH                      | Reserved                    | CAN_MSG1DATA7        |  |  |

| 1E5CH                                      | CAN_MSG5DATA6           | CAN_MSG5DATA5   | 1E1CH                      | CAN_MSG1DATA6               | CAN_MSG1DATA5        |  |  |

| 1E5AH                                      | CAN_MSG5DATA4           | CAN_MSG5DATA3   | 1E1AH                      | CAN_MSG1DATA4               | CAN_MSG1DATA3        |  |  |

| 1E58H                                      | CAN_MSG5DATA2           | CAN_MSG5DATA1   | 1E18H                      | CAN_MSG1DATA2               | CAN_MSG1DATA1        |  |  |

| 1E56H                                      | CAN_MSG5DATA0           | CAN_MSG5CFG     | 1E16H                      | CAN_MSG1DATA0               | CAN_MSG1CFG          |  |  |

| 1E54H                                      | CAN_MSG5ID3             | CAN_MSG5ID2     | 1E14H                      | CAN_MSG1ID3                 | CAN_MSG1ID2          |  |  |

| 1E52H                                      | CAN_MSG5ID1             | CAN_MSG5ID0     | 1E12H                      | CAN_MSG1ID1                 | CAN_MSG1ID0          |  |  |

| 1E50H                                      | CAN_MSG5CON1            | CAN_MSG5CON0    | 1E10H                      | CAN_MSG1CON1                | CAN_MSG1CON0         |  |  |

|                                            | Message 4 and Bit       | Timing 1        |                            | Mask, Control, an           | d Status             |  |  |

| Addr                                       | High (Odd) Byte         | Low (Even) Byte | Addr                       | High (Odd) Byte             | Low (Even) Byte      |  |  |

| 1E4EH                                      | CAN_BTIME1 <sup>†</sup> | CAN_MSG4DATA7   | 1E0EH                      | CAN_MSK15                   | CAN_MSK15            |  |  |

| 1E4CH                                      | CAN_MSG4DATA6           | CAN_MSG4DATA5   | 1E0CH                      | CAN_MSK15                   | CAN_MSK15            |  |  |

| 1E4AH                                      | CAN_MSG4DATA4           | CAN_MSG4DATA3   | 1E0AH                      | CAN_EGMSK                   | CAN_EGMSK            |  |  |

| 1E48H                                      | CAN_MSG4DATA2           | CAN_MSG4DATA1   | 1E08H                      | CAN_EGMSK                   | CAN_EGMSK            |  |  |

| 1E46H                                      | CAN_MSG4DATA0           | CAN_MSG4CFG     | 1E06H                      | CAN_SGMSK                   | CAN_SGMSK            |  |  |

| 1E44H                                      | CAN_MSG4ID3             | CAN_MSG4ID2     | 1E04H                      | Reserved                    | Reserved             |  |  |

| 1E42H                                      | CAN_MSG4ID1             | CAN_MSG4ID0     | 1E02H                      | Reserved                    | Reserved             |  |  |

| 1E40H                                      | CAN_MSG4CON1            | CAN_MSG4CON0    | 1E00H                      | CAN_STAT                    | CAN_CON <sup>†</sup> |  |  |

Table 3-4. CAN Peripheral SFRs (Continued)

$^{\dagger}$  The CCE bit in the control register (CAN\_CON) must be set to enable write access to the bit timing registers (CAN\_BTIME0 and CAN\_BTIME1).

| Peripheral                                   | WSR Value for<br>32-byte Window<br>(00E0–00FFH) | WSR Value for<br>64-byte Window<br>(00C0–00FFH) | WSR Value for<br>128-byte Window<br>(0080–00FFH) |  |  |  |

|----------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------|--|--|--|

| Ports 0, 1, 2, 6                             | 7EH                                             | 3FH                                             |                                                  |  |  |  |

| A/D converter, EPA interrupts                | 7DH                                             | 3EH                                             | 1FH                                              |  |  |  |

| EPA compare 0–1, capture/compare 8–9, timers | 7CH                                             | 350                                             |                                                  |  |  |  |

| EPA capture/compare 0-7                      | 7BH                                             | 3DH                                             | 1EH                                              |  |  |  |

| CAN messages 14–15                           | 77H                                             | 3BH                                             |                                                  |  |  |  |

| CAN messages 12–13                           | 76H                                             | ЗБП                                             | 1DH                                              |  |  |  |

| CAN messages 10–11                           | 75H                                             | ЗАН                                             |                                                  |  |  |  |

| CAN messages 8–9                             | 74H                                             | ЗАП                                             |                                                  |  |  |  |

| CAN messages 6–7                             | 73H                                             | 2011                                            |                                                  |  |  |  |

| CAN messages 4–5, bit timing 1, interrupts   | 72H                                             | 39H                                             | 1CH                                              |  |  |  |

| CAN messages 2–3, bit timing 0               | 71H                                             | 38H                                             |                                                  |  |  |  |

| CAN message 1, control, status, mask         | 70H                                             | 301                                             |                                                  |  |  |  |

Table 3-5. Selecting a Window of Peripheral SFRs

| <u>г</u>                  | · · · · · · · · · · · · · · · · · · ·           |                                                 |                                                  |  |  |

|---------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------|--|--|

| Register RAM<br>Locations | WSR Value<br>for 32-byte Window<br>(00E0–00FFH) | WSR Value<br>for 64-byte Window<br>(00C0–00FFH) | WSR Value<br>for 128-byte Window<br>(0080–00FFH) |  |  |

| 03E0-03FFH                | 5FH                                             | 2FH                                             |                                                  |  |  |

| 03C0-03DFH                | 5EH                                             | ZFH                                             | 17H                                              |  |  |

| 03A0-03BFH                | 5DH                                             | 2EH                                             | 1/11                                             |  |  |

| 0380-039FH                | 5CH                                             | ZEH                                             |                                                  |  |  |

| 0360–037FH                | 5BH                                             | 204                                             |                                                  |  |  |

| 0340-035FH                | 5FH 5AH 2DH                                     |                                                 | – 16H                                            |  |  |

| 0320-033FH                | 59H                                             | 2CH                                             | юп                                               |  |  |

| 0300-031FH                | 58H                                             | 2CH                                             |                                                  |  |  |

| 02E0-02FFH                | 57H                                             |                                                 |                                                  |  |  |

| 02C0-02DFH                | 56H                                             | 2BH                                             |                                                  |  |  |

| 02A0-02BFH                | 55H                                             |                                                 |                                                  |  |  |

| 0280-029FH                | 54H                                             | 2AH                                             | 15H                                              |  |  |

| 0260–027FH                | 53H                                             |                                                 |                                                  |  |  |

| 0240-025FH                | 52H                                             | 29H                                             |                                                  |  |  |

| 0220-023FH                | 51H                                             |                                                 |                                                  |  |  |

| 0200–021FH                | 50H                                             | 28H                                             | 14H                                              |  |  |

| 01E0-01FFH                | 4FH                                             |                                                 |                                                  |  |  |

| 01C0-01DFH                | 4EH                                             | 27H                                             |                                                  |  |  |

| 01A0-01BFH                | 4DH                                             |                                                 |                                                  |  |  |

| 0180–019FH                | 4CH                                             | 26H                                             | 13H                                              |  |  |

| 0160–017FH                | 4BH                                             |                                                 |                                                  |  |  |

| 0140–015FH                | 4AH                                             | 25H                                             |                                                  |  |  |

| 0120–013FH                | 49H                                             |                                                 |                                                  |  |  |

| 0100–011FH                | 48H                                             | 24H                                             | 12H                                              |  |  |

#### Table 3-6. Selecting a Window of the Upper Register File

|                                                                                   | WSR Value | WSR Value                          | WSR Value                           |  |

|-----------------------------------------------------------------------------------|-----------|------------------------------------|-------------------------------------|--|

| Register RAM<br>Locations         WSK Value<br>for 32-byte Window<br>(00E0–00FFH) |           | for 64-byte Window<br>(00C0–00FFH) | for 128-byte Window<br>(0080–00FFH) |  |

| 0DE0-0DFFH                                                                        | 6FH       | 37Н                                |                                     |  |

| 0DC0-0DDFH                                                                        | 6EH       | 37日                                | 1BH                                 |  |

| 0DA0-0DBFH                                                                        | 6DH       | - 36H                              | івп                                 |  |

| 0D80-0D9FH                                                                        | 6CH       | 30П                                |                                     |  |

| 0D60-0D7FH                                                                        | 6BH       | - 35H                              | - 1AH                               |  |

| 0D40-0D5FH                                                                        | 6AH       | 35日                                |                                     |  |

| 0D20-0D3FH                                                                        | 69H       | - 34H                              | ТАП                                 |  |

| 0D00-0D1FH                                                                        | 68H       | 34⊓                                |                                     |  |

| 0CE0-0CFFH                                                                        | 67H       | 33Н                                |                                     |  |

| 0CC0-0CDFH                                                                        | 66H       | 33⊓                                | 19H                                 |  |

| 0CA0-0CBFH                                                                        | 65H       | 32H                                | 19⊓                                 |  |

| 0C80-0C9FH                                                                        | 64H       | 32日                                |                                     |  |

| 0C60-0C7FH                                                                        | 63H       | 214                                |                                     |  |

| 0C40-0C5FH                                                                        | 62H       | - 31H                              |                                     |  |

| 0C20-0C3FH                                                                        | 61H       | 2011                               | 18H                                 |  |

| 0C00-0C1FH                                                                        | 60H       | - 30H                              |                                     |  |

Table 3-7. Selecting a Window of Upper Register RAM

|                  | Table 5-6. Windows                              |                                                 |                                                  |  |  |  |  |  |

|------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------|--|--|--|--|--|

| Base Address     | WSR Value<br>for 32-byte Window<br>(00E0–00FFH) | WSR Value<br>for 64-byte Window<br>(00C0–00FFH) | WSR Value for<br>128-byte Window<br>(0080–00FFH) |  |  |  |  |  |

| Peripheral SFRs  |                                                 | ·                                               |                                                  |  |  |  |  |  |

| 1FE0H            | 7FH †                                           |                                                 |                                                  |  |  |  |  |  |

| 1FC0H            | 7EH                                             | 3FH †                                           |                                                  |  |  |  |  |  |

| 1FA0H            | 7DH                                             |                                                 |                                                  |  |  |  |  |  |

| 1F80H            | 7CH                                             | 3EH                                             | 1FH †                                            |  |  |  |  |  |

| 1F60H            | 7BH                                             |                                                 |                                                  |  |  |  |  |  |

| 1F40H            | 7AH                                             | 3DH                                             |                                                  |  |  |  |  |  |

| 1F20H            | 79H                                             |                                                 |                                                  |  |  |  |  |  |

| 1F00H            | 78H                                             | 3CH                                             | 1EH                                              |  |  |  |  |  |

| CAN Peripheral S | FRs                                             |                                                 |                                                  |  |  |  |  |  |

| 1EE0H            | 77H                                             |                                                 |                                                  |  |  |  |  |  |

| 1EC0H            | 76H                                             | ЗВН                                             |                                                  |  |  |  |  |  |

| 1EA0H            | 75H                                             |                                                 |                                                  |  |  |  |  |  |

| 1E80H            | 74H                                             | ЗАН                                             | 1DH                                              |  |  |  |  |  |

| 1E60H            | 73H                                             |                                                 |                                                  |  |  |  |  |  |

| 1E40H            | 72H                                             | 39H                                             |                                                  |  |  |  |  |  |

| 1E20H            | 71H                                             |                                                 |                                                  |  |  |  |  |  |

| 1E00H            | 70H                                             | 38H                                             | 1CH                                              |  |  |  |  |  |

| Register RAM     |                                                 |                                                 |                                                  |  |  |  |  |  |

| 1DE0H            | 6FH                                             |                                                 |                                                  |  |  |  |  |  |

| 1DC0H            | 6EH                                             | 37H                                             |                                                  |  |  |  |  |  |

| 1DA0H            | 6DH                                             |                                                 |                                                  |  |  |  |  |  |

| 1D80H            | 6CH                                             | 36H                                             | 1BH                                              |  |  |  |  |  |

| 1D60H            | 6BH                                             |                                                 |                                                  |  |  |  |  |  |

| 1D40H            | 6AH                                             | 35H                                             |                                                  |  |  |  |  |  |

| 1D20H            | 69H                                             |                                                 |                                                  |  |  |  |  |  |

| 1D00H            | 68H                                             | 34H                                             | 1AH                                              |  |  |  |  |  |

| 1CE0H            | 67H                                             |                                                 |                                                  |  |  |  |  |  |

| 1CC0H            | 66H                                             | 33H                                             |                                                  |  |  |  |  |  |

| 1CA0H            | 65H                                             |                                                 |                                                  |  |  |  |  |  |

| 1C80H            | 64H                                             | 32H                                             | 19H                                              |  |  |  |  |  |

| 1C60H            | 63H                                             |                                                 |                                                  |  |  |  |  |  |

| 1C40H            | 62H                                             | 31H                                             |                                                  |  |  |  |  |  |

| 1C20H            | 61H                                             |                                                 |                                                  |  |  |  |  |  |

| 1C00H            | 60H                                             | 30H                                             | 18H                                              |  |  |  |  |  |

| Table 3-8. Windows | Tabl | e 3-8. | Wind | lows |

|--------------------|------|--------|------|------|

|--------------------|------|--------|------|------|

<sup>†</sup> Locations 1FE0–1FFFH contain memory-mapped SFRs that cannot be accessed through a window. Reading these locations through a window returns FFH; writing these locations through a window has no effect.

| Base Address      | WSR Value<br>for 32-byte Window<br>(00E0–00FFH) | WSR Value<br>for 64-byte Window<br>(00C0–00FFH) | WSR Value for<br>128-byte Window<br>(0080–00FFH) |  |

|-------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------|--|

| Upper Register Fi | le                                              |                                                 |                                                  |  |

| 03E0H             | 5FH                                             |                                                 |                                                  |  |

| 03C0H             | 5EH                                             | 2FH                                             |                                                  |  |

| 03A0H             | 5DH                                             |                                                 |                                                  |  |

| 0380H             | 5CH                                             | 2EH                                             | 17H                                              |  |

| 0360H             | 5BH                                             |                                                 |                                                  |  |

| 0340H             | 5AH                                             | 2DH                                             |                                                  |  |

| 0320H             | 59H                                             |                                                 |                                                  |  |